## SGM41281/SGM41281C 70V/35V 2.5mA Precise Protection APD Bias Dual-Gains Current Mirror w/ Output Enable

## **GENERAL DESCRIPTION**

The SGM41281 or the SGM41281C integrates a boost for generating up to 70V regulated output, a dual-gains current mirror with a controlled output buffer, which is unique to simplify the multi-channel receiving monitoring sharing design with a MCU with regular resolution ADC. Its precise over current protection and mirror voltage drop compensation further make design tradeoff comfortable between more sensitivity and more robust.

The SGM41281 is available in Green TQFN-3×3-16L package and the SGM41281C is available in Green 12-Bump, 1.2mm × 1.6mm, 0.4mm Pitch WLCSP package. Both operate over an ambient temperature range of -40°C to +85°C.

## **FEATURES**

- Up to 70V Output 1.3MHz Boost Regulator

- 1:30 Output Voltage Programming

- Programmable Precise Over Current Limit

Protection

- Compensated Mirror Voltage Drop

- Internal X1/X16 Dual Gain Current Mirror

- 2.5V Full Scale Current to Voltage Buffer

- Full Chain Circuit: Bias-Mirror-Track/Hold

- Controlled Monitoring Outputs for Sharing

- SGM41281 Available in Green TQFN-3×3-16L Package

- SGM41281C Available in Green 12-Bump, 1.2mm × 1.6mm, 0.4mm Pitch WLCSP Package

- -40°C to +85°C Operating Temperature Range

## **APPLICATIONS**

CWDM/DWDM Fiber Modules CFP Modules

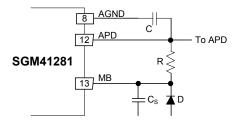

## TYPICAL APPLICATION

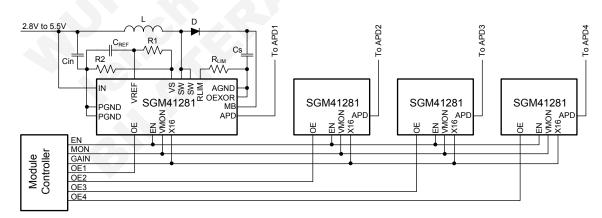

Figure 1. Typical Application Circuit

## **PACKAGE/ORDERING INFORMATION**

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

| SGM41281  | TQFN-3×3-16L           | -40°C to +85°C                    | SGM41281YTQ16G/TR  | 41281TQ<br>XXXXX   | Tape and Reel, 4000 |

| SGM41281C | WLCSP                  | -40°C to +85°C                    |                    |                    |                     |

NOTE: XXXXX = Date Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### **ABSOLUTE MAXIMUM RATINGS**

IN, EN, VS, OE, VMON, RLIM, VREF, X16, OEXOR

|                                    | 0.3V to 6V          |

|------------------------------------|---------------------|

| SW, MB                             | 0.3V to 76V         |

| APD                                | 0.3V to (MB + 0.3V) |

| Storage Temperature Range          | 65°C to +150°C      |

| Lead Temperature (Soldering, 10s). | +260°C              |

### **RECOMMENDED OPERATING CONDITIONS**

| Supply Voltage Range             | 2.8V to 5.5V   |

|----------------------------------|----------------|

| V <sub>APD</sub> Range, SGM41281 | 20V to 70V     |

| VAPD Range, SGM41281C            | 15V to 35V     |

| I <sub>APD</sub>                 | <2mA           |

| Junction Temperature Range       | 40°C to +125°C |

| Environmental Temperature Range  | 40°C to +85°C  |

### **OVERSTRESS CAUTION**

Stresses beyond those listed may cause permanent damage to the device. Functional operation of the device at these or any other conditions beyond those indicated in the operational section of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time.

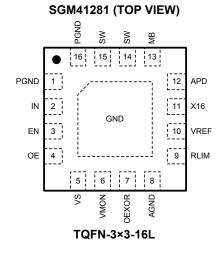

## **PIN CONFIGURATIONS**

### SGM41281C (TOP VIEW)

WLCSP

## **PIN DESCRIPTION**

| PIN          |       |       | $\mathbf{T}$        | FUNCTION                                                                                                                                                                                                                                                                     |

|--------------|-------|-------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN-3×3-16L | WLCSP | NAME  | TYPE <sup>(1)</sup> | FUNCTION                                                                                                                                                                                                                                                                     |

| 1, 16        | A3    | PGND  | G                   | Ground, current return path of the boost switch.                                                                                                                                                                                                                             |

| 2            | В3    | IN    | Р                   | Power Input to all Internal Circuit. A $4.7\mu$ F or over high frequency type capacitor placed close to IN and PGND is recommended.                                                                                                                                          |

| 3            | B2    | EN    | I                   | Enable Input. Input high to enable this chip, low to shut down.                                                                                                                                                                                                              |

| 4            | C3    | OE    | Г                   | Output Enable. Its effective logic level is decided by the logic level seen at the OEXOR input. If the (OE xor OEXOR) is true, enables the VMON and X16 to output, or both are put into high-Z state otherwise.                                                              |

| 5            | D3    | VS    | L.                  | Proportional input for programming the MB voltage with an increment gain of 1:30.                                                                                                                                                                                            |

| 6            | D2    | VMON  | 0                   | Current Monitoring Output, which is a voltage proportional to the current out of the APD pin.                                                                                                                                                                                |

| 7            | -     | OEXOR |                     | Logic input; for selecting effective logic level of output enabling at the OE input. The<br>complementary logic level to the logic level of the OEXOR at the OE is put for tracking.                                                                                         |

| 8            | D1    | AGND  | G                   | Ground; current return path of the current sensing circuit.                                                                                                                                                                                                                  |

| 9            | C2    | RLIM  |                     | Current-Limit Programming. Connect a resistor from RLIM to GND to program the APD current-limit threshold.                                                                                                                                                                   |

| 10           | -     | VREF  | 0                   | 2.5V Voltage Reference Output.                                                                                                                                                                                                                                               |

| 11           | C1    | X16   | 0                   | Gain Selection Output. The current monitoring circuit selects internal X1 or X16 stage<br>adaptively against the current level for extending the monitoring scale by 16 times over a given<br>an ADC type. Output high for reporting that the X16 gain stage is selected.    |

| 12           | B1    | APD   | 0                   | Output for Biasing the APD Device. The current out of this pin is sampled with a mirror circuit for current monitoring and over current protection. The voltage drop over the mirror stage is compensated against the current change, which maintains the drop varying less. |

| 13           | A1    | MB    | I                   | Mirror Bias Input. Connected to the boost stage output.                                                                                                                                                                                                                      |

| 14, 15       | A2    | SW    | 0                   | Low End Boost Switch Output. Connect to the anode of the rectifier diode and the boost end of a power inductor.                                                                                                                                                              |

| Exposed Pad  | -     | GND   | G                   | Ground; internally tie to substrate of the circuit.                                                                                                                                                                                                                          |

NOTE : I: input, O: output, G: ground, P: power for the circuit.

## **ELECTRICAL CHARACTERISTICS**

(Test at  $T_A = +25^{\circ}$ C,  $V_{IN} = 3.3$ V, EN =  $V_{IN}$ ,  $V_{FS} = 70$ V for the SGM41281,  $V_{FS} = 35$ V for the SGM41281C, unless otherwise specified in test conditions. Limits in boldface type apply over the entire junction temperature range for operation. Limits are production tested, and highly appreciate values on characterization and statistics.)

| PARAMETERS                                           | SYMBOL                         | CONDITIONS                                                | MIN | TYP  | MAX | UNITS |

|------------------------------------------------------|--------------------------------|-----------------------------------------------------------|-----|------|-----|-------|

| Supply Voltage Range                                 | V <sub>IN</sub>                |                                                           | 2.8 |      | 5.5 | V     |

| Efficiency                                           | η                              | 70V 1mA loading                                           |     |      |     |       |

| Quiescent Current                                    | Ι <sub>Q</sub>                 |                                                           |     | 1.3  |     | mA    |

| Under-Voltage Lockout Threshold                      | V <sub>UVLO</sub>              | V <sub>IN</sub> rising                                    |     | 2.5  |     | V     |

| Under-Voltage Lockout Hysteresis                     | $V_{\text{UVLO}_{\text{HYS}}}$ |                                                           |     | 200  |     | mV    |

| Shutdown Current                                     | I <sub>SHDN</sub>              | V <sub>SHDN</sub> = 0V                                    |     | 0.02 |     | μA    |

| Output Short Circuit Operation Current               | I <sub>SHRT</sub>              |                                                           |     |      |     |       |

| BOOST AND APD BIASING                                |                                |                                                           |     |      |     |       |

| Switch Frequency                                     | f <sub>SW</sub>                |                                                           |     | 1.3  |     | MHz   |

| Maximum Duty Cycle                                   | D <sub>MAX</sub>               |                                                           |     | 90   |     | %     |

| $V_{\text{VS}}$ to $V_{\text{MB}}$ Programming Ratio | VPR                            |                                                           |     | 30   |     |       |

| Boost Start-Up Time                                  | t <sub>UP</sub>                | From EN to 90% 70V output voltage, 1mA load               |     | 1    |     | ms    |

| Power Switch on Resistance                           | R <sub>ON</sub>                |                                                           |     | 0.6  |     | Ω     |

| Peak Switch Current Limit                            | I <sub>LIM_SW</sub>            |                                                           |     | 1.1  |     | А     |

| Switch Leakage Current                               |                                | V <sub>SW</sub> = 76V, T <sub>A</sub> = +25°C             |     | 0.1  |     | μA    |

| Mirror Voltage Drop                                  | V <sub>MD01</sub>              | 100µA loading, 70V                                        |     | 2.4  |     | v     |

| Mirror Voltage Drop                                  | V <sub>MD1</sub>               | 1mA loading, 70V                                          |     | 2.5  |     | v     |

| $V_{\text{IN}}$ to $V_{\text{APD}}$ Suppression      | SRAPD                          | Test by applying 0.1V 1kHz square wave at V <sub>IN</sub> |     |      |     | %     |

| $V_{\text{IN}}$ to $V_{\text{MB}}$ Suppression       | SR <sub>MB</sub>               | Test by applying 0.1V 1kHz square wave at V <sub>IN</sub> |     |      |     | %     |

| CURRENT MONITORING                                   |                                |                                                           |     |      |     |       |

| 1X Transfer Resistance                               | TR <sub>1X</sub>               | APD current to VMON transferring ratio, X1                |     | 1.25 |     | kΩ    |

| 16X Transfer Resistance                              | TR <sub>16X</sub>              | APD current to VMON transferring ratio, X16               |     | 20   |     | kΩ    |

| Gain Difference Error                                | G <sub>DE</sub>                | X1 to X16 gain ratio variation                            |     |      |     |       |

| Low Gain Change Point                                | LG <sub>CP</sub>               | X1 to X16 gain change, VMON after rising                  |     |      |     |       |

| High Gain Change Point                               | HG <sub>CP</sub>               | X16 to X1 gain change, VMON after falling                 |     |      |     |       |

| X1 In-Scale Error                                    | 1X <sub>ERROR</sub>            | From change point to 90% X1 FS                            |     |      |     |       |

| X16 In-Scale Error                                   | 16X <sub>ERROR</sub>           | From 10% X16 FS to change point                           |     |      |     |       |

| Full Range Error                                     | FR <sub>ERROR</sub>            | Full range error, from 10% X16 FS to 90% X1 FS            |     |      |     |       |

| Monitoring Settle Time                               | t <sub>st</sub>                | APD to VMON settle time, to 90%                           |     | 250  |     | ns    |

| Holding Droop                                        | VDROOP                         |                                                           |     |      |     |       |

| VMON Ripple at Tracking                              | VR <sub>TRK</sub>              | Tracking, $C_s 0.1 \mu F$ , 1mA 70V load                  |     | 50   |     | mv    |

| VMON Ripple at Holding                               | VR <sub>HLD</sub>              | Holding, C <sub>s</sub> 0.1µF, 1mA 70V load               |     |      |     |       |

| VMON PSSR at Tracking                                | PSSRTRK                        | Tracking, applying 0.1V 1kHz at V <sub>IN</sub>           |     |      |     |       |

| VMON PSSR at Holding                                 | PSSR <sub>HLD</sub>            | Holding, applying 0.1V 1kHz at V <sub>IN</sub>            |     |      |     |       |

| ILIM Programming Error                               | ILIMERR                        | Test with $R_{LIM} = 28k\Omega$ for $I_{LIM} = 2.5mA$     |     |      |     |       |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Test at  $T_A = +25^{\circ}$ C,  $V_{IN} = 3.3$ V, EN =  $V_{IN}$ ,  $V_{FS} = 70$ V for the SGM41281,  $V_{FS} = 35$ V for the SGM41281C, unless otherwise specified in test conditions. Limits in boldface type apply over the entire junction temperature range for operation. Limits are production tested, and highly appreciate values on characterization and statistics.)

| PARAMETERS                   | SYMBOL          | CONDITIONS              | MIN | TYP | MAX | UNITS |

|------------------------------|-----------------|-------------------------|-----|-----|-----|-------|

| LOGIC IO                     |                 |                         |     |     |     |       |

| Input Low Threshold          | V <sub>IL</sub> |                         |     |     | 0.4 | V     |

| Input High Threshold         | V <sub>IH</sub> |                         | 1.6 |     |     | V     |

| Input Low Souring            | I <sub>LS</sub> | Bias to V <sub>IL</sub> |     | 1   |     | nA    |

| THERMAL PROTECTION           |                 |                         |     |     |     |       |

| Thermal Shutdown Temperature |                 | Temperature rising      |     | 160 |     | °C    |

| Thermal Shutdown Hysteresis  |                 |                         |     | 15  |     | °C    |

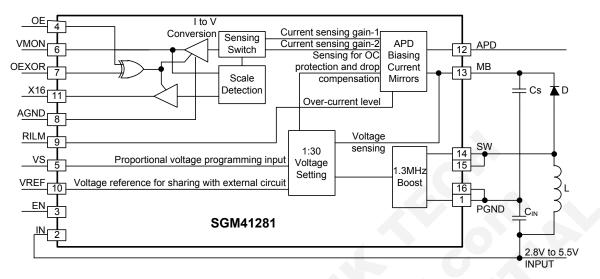

## FUNCTIONAL BLOCK DIAGRAM

Figure 2. Circuit Block Diagram

## **OUTPUT SETTLING**

插入实测波形替换

调整电流使 VMON 输出 500mV 左右, X16=1;在 VMON 和 X16 均挂 1k 负载。

Figure 3. ON to VMON and X16 Settlings (OEXOR = L)

# SGM4128170V/35V 2.5mA Precise Protection APD BiasSGM41281CDual-Gains Current Mirror w/ Output Enable

## FUNCTION, OPERATION AND APPLICATION

Ref to the Figure 2 for more details, the SGM41281 has 4 elementary circuits. One is for programming the output voltage and compensating the voltage drop on the mirror circuit; one is for generating a higher voltage from low voltage power source; one is a current mirror that samples the current out of APD pin into internal circuit for monitoring and protection; and the last one is a current to voltage converter and a dual-gains adaptive buffer circuit that selects a proper gain for outputting against APD current level.

## Extending the Appreciated Monitoring Range

The VMON buffer circuit could select a proper gain for outputting a suitable signal for external circuit and a flag signal to report which gain selected adaptively by check if the APD current is too low or too high to a given range. This design extends the appreciated monitoring range by 16 times. As the fiber receiver monitors signal in very high dynamic range but less resolution, this circuit is a unique tradeoff between the resolution and dynamic range.

### Programming the APD Voltage

The voltage seen at the APD pin is the sum of a component proportional to the setting voltage at the VS pin and a headroom drop designed for the current mirror operation. The voltage at APD pin and the voltage at the MB pin are calculated with following equations, where the  $V_{APD}$  is the voltage seen at the APD pin, the VMB is the voltage at the BM pin, the  $V_{VS}$  is the voltage put at the VS pin and the  $I_{APD}$  is the current out of the APD pin; also reference to the typical VI plots in the Figure 4:

$$V_{PAD} = XX(V_{VS}), YY(I_{APD})$$

$V_{BM} = ?????$

此处插入图 4,在 V<sub>APD</sub>和 V<sub>VS</sub>为轴的坐标中绘制几个不 同电流时 V<sub>VS</sub>与 V<sub>MB</sub>和 V<sub>APD</sub>的关系

Figure 4. The  $V_{\text{VS}}$  to  $V_{\text{APD}}$  and  $V_{\text{MB}}$  plots

### Programming the Current Limit Level

The RLIM for setting the current limit level is calculated with following equation, and the typical  $I_{\text{LIM}}$  to  $R_{\text{LIM}}$  plot is in the Figure 5.

$$\mathsf{R}_{_\mathsf{RLIM}}(\mathsf{k}\Omega) = \frac{70}{\mathsf{I}_{_\mathsf{APD,MAX}}}(\mathsf{m}\mathsf{A})$$

此处插入 ILIM 与 RLIM 的关系曲线

### **Ripple Filtering**

A simple RC filtering circuit could help in suppression of ripple applied at MB input, which then improving the modulation effect to the signal picked-up in the optical channel, which helps in getting better eye diagram opening. Reference to the Figure 6, the resistance of the R inserts drop that is not compensated.

Figure 6. A RC Filtering for Ripple Suppression

## FUNCTION, OPERATION AND APPLICATION (continued)

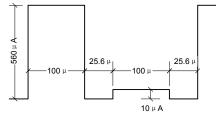

### **Burst Pulse Response**

The Figure 7 shows the capture of waveform at the VMON pin in tracking mode, where a train of current pulses with two different peak values is applied to the APD output, representing the case of burst pulse receiving. The Figure 8 shows the test setup for making the measurement.

### 用获取的变幅度脉冲串输入时的输入、输出波形取代下图

Figure 7. Burst Pulse Receiving Waveform

### **External Components Selection**

### **Components Recommended:**

| CIN | 填入电容容量范围和规格。          |  |  |  |  |  |

|-----|-----------------------|--|--|--|--|--|

| Cs  | 填入电容容量范围和规格。          |  |  |  |  |  |

| 1   | 填入电感量范围和规格。如果跟最大电流有一定 |  |  |  |  |  |

| L   | 关系,在这说明下。             |  |  |  |  |  |

| D   | 填入我们使用的二极管型号。         |  |  |  |  |  |

| R   | 填入电阻范围。               |  |  |  |  |  |

| С   | 填入电容容量范围和规格。          |  |  |  |  |  |

As the boost circuit works at about 1.3MHz, capacitors with good high frequency performance are needed for the application circuit. As the storage capacitor (the  $C_s$  in the Figure 1 or the Figure 2) works with high bias voltage, refer to the capacitor's datasheet to assure its effective capacitance is more than  $0.1\mu$ F at the output voltage.

此处插入测试电路和设备连接图

Figure 8. The Burst Pulse Test Setup

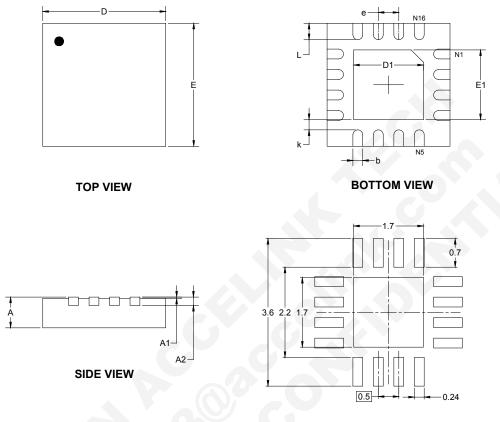

## PACKAGE OUTLINE DIMENSIONS

## TQFN-3×3-16L

#### RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol      |       | nsions<br>meters | Dimensions<br>In Inches |       |  |  |

|-------------|-------|------------------|-------------------------|-------|--|--|

| C y lind of | MIN   | MAX              | MIN                     | MAX   |  |  |

| Α           | 0.700 | 0.800            | 0.028                   | 0.031 |  |  |

| A1          | 0.000 | 0.050            | 0.000                   | 0.002 |  |  |

| A2          | 0.203 | B REF            | 0.008                   | REF   |  |  |

| D           | 2.900 | 3.100            | 0.114                   | 0.122 |  |  |

| D1          | 1.600 | 1.800            | 0.063                   | 0.071 |  |  |

| E           | 2.900 | 3.100            | 0.114                   | 0.122 |  |  |

| E1          | 1.600 | 1.800            | 0.063                   | 0.071 |  |  |

| k           | 0.200 | ) MIN            | 0.008 MIN               |       |  |  |

| b           | 0.180 | 0.300            | 0.007                   | 0.012 |  |  |

| е           | 0.500 | ) TYP            | 0.020                   | TYP   |  |  |

| L           | 0.300 | 0.500            | 0.012                   | 0.020 |  |  |

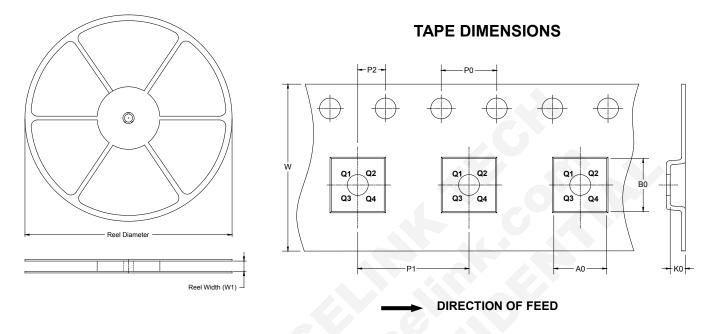

## TAPE AND REEL INFORMATION

### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### KEY PARAMETER LIST OF TAPE AND REEL

| Package Type | Reel<br>Diameter | Reel<br>Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|-----------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TQFN-3×3-16L | 13″              | 12.4                        | 3.35       | 3.35       | 1.13       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-----------|----------------|---------------|----------------|--------------|--------|

| 13″       | 386            | 280           | 370            | 5            | DD0002 |