## SGM41299B

## 3A Thermoelectric Cooler (TEC) Controller

#### GENERAL DESCRIPTION

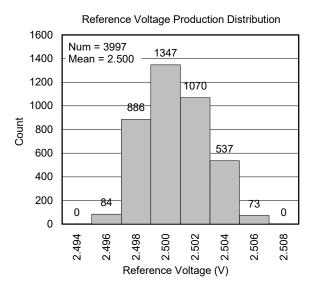

The SGM41299B is a monolithic thermoelectric cooling (TEC) thermostat driver device with two-stage feedback amplifier. The device includes a differential driver (output) stage, an internal 2.5V output reference voltage and two zero-drift, rail-to-rail chopper amplifiers. The first chopper amplifier biases the sensed temperature signal and another is an error amplifier for compensating the closed loop temperature control. This amplifier can be used with a digital controller as well.

The TEC is driven differentially between a linear push-pull stage and a pulse-width modulation (PWM) switching stage. A linear push-pull stage forms one of the arms of the differential output which has a relatively high gain and saturates if the error signal is not close to zero (> 2.5%). This means that the TEC is effectively driven by the other arm. The other arm has a lower gain, and high frequency PWM switching driver that can drive the TEC with high efficiency. The PWM switching driver output is passed through an LC filter to remove large voltage ripple before reaching the TEC. It can sink or source current for both the heating and cooling modes connected to the TEC and stabilize its temperature at the set point.

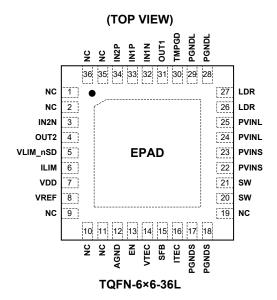

The SGM41299B is available in a Green TQFN-6×6-36L package. It operates over the -40°C to +125°C junction temperature range.

#### **FEATURES**

- High Efficiency Single Inductor Architecture

- Integrated Low R<sub>DSON</sub> MOSFETs for the TEC Controller

- TEC Voltage and Current Monitoring

- No External Sense Resistor Required

- Independent Heating and Cooling Current-Limit Settings Programmable Maximum TEC Voltage

- PWM Driver Switching Frequency: 2.0MHz (TYP)

- Two Zero-Drift, Rail-to-Rail Chopper Amplifiers

- Compatible with NTC or RTD Thermal Sensors

- 2.5V Output Reference Voltage

- Temperature Lock Indicator

- Available in a Green TQFN-6×6-36L Package

#### **APPLICATIONS**

TEC Temperature Controls

Optical Modules

Optical Fiber Amplifiers

Optical Networking Systems

Instruments Requiring TEC Temperature Controls

#### PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER  | PACKAGE<br>MARKING           | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|---------------------|------------------------------|---------------------|

| SGM41299B | TQFN-6×6-36L           | -40°C to +125°C                   | SGM41299BXTQR36G/TR | SGM41299B<br>XTQR36<br>XXXXX | Tape and Reel, 3000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### ABSOLUTE MAXIMUM RATINGS

| PVINL to PGNDL                       | 0.3V to 6V                 |

|--------------------------------------|----------------------------|

| PVINS to PGNDS                       | 0.3V to 6V                 |

| LDR to PGNDL                         | 0.3V to V <sub>PVINL</sub> |

| SW to PGNDS                          | 0.3V to 6V                 |

| AGND to PGNDL                        | 0.3V to 0.3V               |

| AGND to PGNDS                        | 0.3V to 0.3V               |

| VREF, SFB, VLIM_nSD, ILIM, IN1P, IN1 | IN, IN2P, IN2N and         |

| EN to AGND                           | $-0.3V$ to $V_{DD} + 0.3V$ |

| VDD, OUT1, OUT2, ITEC and VTEC to A  | GND0.3V to 6V              |

| Maximum Current                      |                            |

| VREF to AGND                         | 20mA                       |

| OUT1, OUT2, ITEC and VTEC to AGND.   | 50mA                       |

| Package Thermal Resistance           |                            |

| TQFN-6×6-36L, θ <sub>JA</sub>        | 28°C/W                     |

| Junction Temperature                 | +150°C                     |

| Storage Temperature Range            | 65°C to +150°C             |

| Lead Temperature (Soldering, 10s)    | +260°C                     |

| ESD Susceptibility                   |                            |

| HBM                                  |                            |

| CDM                                  | 1000V                      |

|                                      |                            |

#### **RECOMMENDED OPERATING CONDITIONS**

| Driver Supply Voltage Range           | 2.7V to 5.5V   |

|---------------------------------------|----------------|

| Controller Supply Voltage Range       | 2.7V to 5.5V   |

| Operating Ambient Temperature Range4  | 10°C to +125°C |

| Operating Junction Temperature Range4 | 10°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

#### **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN                            | NAME     | FUNCTION                                                                                                                                                                     |

|--------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 9, 10,<br>11, 19, 35, 36 | NC       | No Connection. Leave these pins floating.                                                                                                                                    |

| 3                              | IN2N     | Inverting Input of the A2 (Compensation) Amplifier.                                                                                                                          |

| 4                              | OUT2     | Output of the A2 (Compensation) Amplifier.                                                                                                                                   |

| 5                              | VLIM_nSD | Voltage Limit/Shutdown Input. This pin sets the cooling and heating TEC voltage limits (positive or negative TEC voltage limit). If it is pulled low, the device shuts down. |

| 6                              | ILIM     | Current Limit Setting Input. This pin sets the TEC cooling and heating current limits.                                                                                       |

| 7                              | VDD      | Power Input for the Device.                                                                                                                                                  |

| 8                              | VREF     | 2.5V Reference Output.                                                                                                                                                       |

| 12                             | AGND     | Signal Ground.                                                                                                                                                               |

| 13                             | EN       | Enable. Should be set high to enable the device.                                                                                                                             |

| 14                             | VTEC     | TEC Voltage Monitoring Output.                                                                                                                                               |

| 15                             | SFB      | Feedback Input of the PWM TEC Controller Output Voltage (After LC Filter).                                                                                                   |

| 16                             | ITEC     | TEC Current Monitoring Output.                                                                                                                                               |

| 17, 18                         | PGNDS    | Power Ground of the PWM Driver Arm.                                                                                                                                          |

| 20, 21                         | SW       | Switch Node Output of the PWM Driver Arm.                                                                                                                                    |

| 22, 23                         | PVINS    | Power Supply Input for the PWM Driver Arm.                                                                                                                                   |

| 24, 25                         | PVINL    | Power Supply Input for the Linear Driver Arm.                                                                                                                                |

| 26, 27                         | LDR      | Output of the Linear Driver Arm.                                                                                                                                             |

| 28, 29                         | PGNDL    | Power Ground of the Linear Driver Arm.                                                                                                                                       |

| 30                             | TMPGD    | Temperature-Good Output.                                                                                                                                                     |

| 31                             | OUT1     | Output of the A1 Amplifier.                                                                                                                                                  |

| 32                             | IN1N     | Inverting Input of the A1 Amplifier.                                                                                                                                         |

| 33                             | IN1P     | Non-Inverting Input of the A1 Amplifier.                                                                                                                                     |

| 34                             | IN2P     | Non-Inverting Input of the A2 (Compensation) Amplifier.                                                                                                                      |

| Exposed Pad                    | EP       | Exposed Pad. Solder the exposed pad to the analog ground plane on the board.                                                                                                 |

## **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 2.7 \text{V to } 5.5 \text{V}, T_J = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ all typical values are measured at } T_J = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                                         | SYMBOL                    | CONDITIONS                                        | MIN  | TYP                      | MAX  | UNITS |

|---------------------------------------------------|---------------------------|---------------------------------------------------|------|--------------------------|------|-------|

| Power Supply                                      |                           |                                                   |      |                          |      |       |

| Driver Supply Voltage                             | $V_{PVIN}$                |                                                   | 2.7  | T                        | 5.5  | Ιv    |

| Controller Supply Voltage                         | V <sub>DD</sub>           |                                                   | 2.7  |                          | 5.5  | V     |

| V <sub>DD</sub> Over-Voltage Protection Threshold | V <sub>OVP</sub>          |                                                   | 5.56 | 5.75                     | 5.95 | V     |

| OVP Hysteresis                                    | V OVP                     | T <sub>J</sub> = +25°C                            | 15   | 35                       | 50   | mV    |

| Supply Current                                    | I <sub>DD</sub>           | PWM not switching                                 | 10   | 1.3                      | 2    | mA    |

| Shutdown Current                                  | I <sub>SD</sub>           | EN = AGND or VLIM nSD = AGND                      |      | 200                      | 350  | μA    |

| Under-Voltage Lockout (UVLO)                      | V <sub>UVLO</sub>         | V <sub>DD</sub> rising                            | 2.50 | 2.58                     | 2.66 | V     |

| UVLO Hysteresis                                   | V <sub>UVLO_HYST</sub>    | V <sub>DD</sub> rising                            | 2.00 | 90                       | 2.00 | mV    |

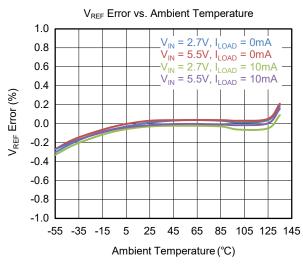

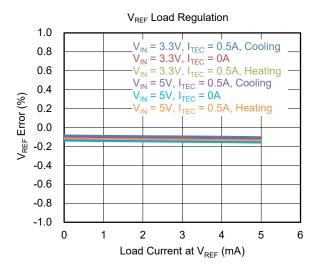

| Reference Voltage                                 | V UVLO_HYST               | I <sub>REF</sub> = 0mA to 10mA                    | 2.47 | 2.50                     | 2.53 | V     |

| Linear Output                                     | V REF                     | IREF - OTTA TO TOTTA                              | 2.47 | 2.50                     | 2.55 | V     |

| •                                                 |                           |                                                   |      | 0                        |      | Ιv    |

| Low Output Voltage                                | $V_{LDR}$                 | I <sub>LDR</sub> = 0A                             |      |                          |      |       |

| High Output Voltage                               |                           | 7 .0500                                           | 0.5  | V <sub>PVIN</sub>        |      | V     |

| Maximum Source Current                            | I <sub>LDR_SOURCE</sub>   | T <sub>J</sub> = +25°C                            | 3.5  |                          |      | A     |

| Maximum Sink Current                              | I <sub>LDR_SINK</sub>     | T <sub>J</sub> = +25°C                            |      | 50                       | 3.5  | Α     |

| P-MOSFET On-Resistance                            | R <sub>DS_PL(ON)</sub>    | I <sub>LDR</sub> = 1.5A, V <sub>PVIN</sub> = 5.0V |      | 50                       | 90   | mΩ    |

|                                                   |                           | I <sub>LDR</sub> = 1.5A, V <sub>PVIN</sub> = 3.3V |      | 58                       | 100  | 1     |

| N-MOSFET On-Resistance                            | R <sub>DS_NL(ON)</sub>    | $I_{LDR} = 1.5A, V_{PVIN} = 5.0V$                 |      | 47                       | 95   | mΩ    |

|                                                   | = \' '                    | $I_{LDR} = 1.5A, V_{PVIN} = 3.3V$                 |      | 53                       | 105  |       |

| P-MOSFET Leakage Current                          | I <sub>LDR_P_LKG</sub>    |                                                   |      | 0.1                      | 5    | μΑ    |

| N-MOSFET Leakage Current                          | I <sub>LDR_N_LKG</sub>    |                                                   |      | 100                      | 180  | μA    |

| Linear Amplifier Gain                             | $A_{LDR}$                 |                                                   |      | 40                       |      | V/V   |

| LDR Short-Circuit Threshold                       | I <sub>LDR_SH_GNDL</sub>  | LDR short to PGNDL, enter hiccup                  |      | 4.5                      |      | Α     |

|                                                   | I <sub>LDR_SH_PVINL</sub> | LDR short to PVIN, enter hiccup                   |      | -4.5                     |      | Α     |

| Hiccup Cycle                                      | t <sub>HICCUP</sub>       |                                                   |      | 15                       |      | ms    |

| PWM Output                                        |                           |                                                   |      |                          |      |       |

| Low Output Voltage                                | $V_{SFB}$                 | I <sub>SFB</sub> = 0A                             |      | 0.06 × V <sub>PVIN</sub> |      | V     |

| High Output Voltage                               | V SFB                     | I <sub>SFB</sub> = 0A                             |      | $0.93 \times V_{PVIN}$   |      | V     |

| Maximum Source Current                            | I <sub>SW_SOURCE</sub>    | T <sub>J</sub> = +25°C                            | 3.5  |                          |      | Α     |

| Maximum Sink Current                              | I <sub>SW_SINK</sub>      | T <sub>J</sub> = +25°C                            |      |                          | 3.5  | Α     |

| D MOSEET On Desistance                            | Б                         | I <sub>SW</sub> = 1.5A, V <sub>PVIN</sub> = 5.0V  |      | 42                       | 75   | m0    |

| P-MOSFET On-Resistance                            | R <sub>DS_PS(ON)</sub>    | I <sub>SW</sub> = 1.5A, V <sub>PVIN</sub> = 3.3V  |      | 50                       | 85   | mΩ    |

| NAMOSETTO D. 11                                   | Б                         | I <sub>SW</sub> = 1.5A, V <sub>PVIN</sub> = 5.0V  |      | 31                       | 60   | 0     |

| N-MOSFET On-Resistance                            | R <sub>DS_NS(ON)</sub>    | I <sub>SW</sub> = 1.5A, V <sub>PVIN</sub> = 3.3V  |      | 37                       | 70   | mΩ    |

| P-MOSFET Leakage Current                          | I <sub>SW_P_LKG</sub>     |                                                   |      | 0.1                      | 5    | μA    |

| N-MOSFET Leakage Current                          | I <sub>SW_N_LKG</sub>     |                                                   |      | 0.1                      | 5    | μΑ    |

| PWM Duty Cycle                                    | D <sub>SW</sub>           |                                                   | 6    |                          | 93   | %     |

| SFB Input Bias Current                            | I <sub>SFB</sub>          |                                                   |      | 60                       | 100  | μΑ    |

| Internal Oscillator Frequency                     | f <sub>OSC</sub>          | EN high                                           | 1.76 | 2.00                     | 2.24 | MHz   |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 2.7 \text{V to } 5.5 \text{V}, T_J = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ all typical values are measured at } T_J = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                                      | SYMBOL                                | CONDITIONS                                                                        | MIN                    | TYP   | MAX      | UNITS |

|------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------|------------------------|-------|----------|-------|

| PWM Oscillator                                 |                                       |                                                                                   |                        |       | •        |       |

| EN Low Input Voltage                           | V <sub>IL</sub>                       |                                                                                   |                        |       | 0.8      | V     |

| EN High Input Voltage                          | V <sub>IH</sub>                       |                                                                                   | 2.1                    |       |          | V     |

| EN Input Current                               | I <sub>EN</sub>                       |                                                                                   |                        | 0.3   | 1        | μA    |

| Pull-Down Current                              |                                       |                                                                                   |                        | 0.3   | 2        | μA    |

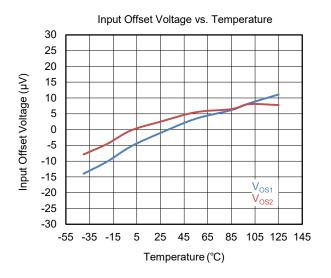

| Error/Compensation Amplifiers                  |                                       |                                                                                   |                        |       |          | •     |

| louist Officet Vallage                         | V <sub>OS1</sub>                      | V <sub>CM1</sub> = 1.5V, V <sub>OS1</sub> = V <sub>IN1P</sub> - V <sub>IN1N</sub> |                        | 10    | 100      | μV    |

| Input Offset Voltage                           | V <sub>OS2</sub>                      | V <sub>CM2</sub> = 1.5V, V <sub>OS2</sub> = V <sub>IN2P</sub> - V <sub>IN2N</sub> |                        | 10    | 100      | μV    |

| Input Voltage Range                            | V <sub>CM1</sub> , V <sub>CM2</sub>   |                                                                                   | 0                      |       | $V_{DD}$ | V     |

| Common Mode Rejection Ratio                    | CMRR                                  | $V_{CM1}$ , $V_{CM2} = 0.2V$ to $V_{DD} - 0.2V$                                   |                        | 120   |          | dB    |

| High Output Voltage                            | V <sub>OH1</sub> , V <sub>OH2</sub>   | I <sub>OUT1</sub> = I <sub>OUT2</sub> = 5mA                                       | V <sub>DD</sub> - 0.15 |       |          | V     |

| Low Output Voltage                             | V <sub>OL1</sub> , V <sub>OL2</sub>   | I <sub>OUT1</sub> = I <sub>OUT2</sub> = 5mA                                       |                        | 90    | 150      | mV    |

| Power Supply Rejection Ratio                   | PSRR                                  |                                                                                   |                        | 120   |          | dB    |

| Output Current                                 | I <sub>OUT1</sub> , I <sub>OUT2</sub> | Sourcing and sinking                                                              | 5                      |       |          | mA    |

| Gain Bandwidth Product                         | GBW                                   | $V_{OUT1}$ , $V_{OUT2} = 0.5V$ to $V_{DD}$ - 1V                                   |                        | 1     |          | MHz   |

| TEC Current Limit                              |                                       |                                                                                   |                        |       |          | •     |

| Current-Limit Threshold (Cooling)              | $V_{ILIMC\_TH}$                       | V <sub>ITEC</sub> = 2V                                                            | 1.98                   | 2.0   | 2.02     | V     |

| Current-Limit Threshold (Heating)              | $V_{ILIMH\_TH}$                       | V <sub>ITEC</sub> = 0.5V                                                          | 0.48                   | 0.50  | 0.52     | V     |

| ILIM Input Current (Cooling)                   | I <sub>ILIMC</sub>                    | Sourcing current                                                                  | 36.5                   | 40    | 43.5     | μA    |

| ILIM Input Current (Heating)                   | I <sub>ILIMH</sub>                    |                                                                                   |                        | 0.01  | 1        | μA    |

| Cooling to Heating Current Detection Threshold | I <sub>COOL_HEAT_TH</sub>             |                                                                                   |                        | 40    |          | mA    |

| TEC Voltage Limit                              |                                       |                                                                                   |                        |       |          |       |

| Voltage Limit Gain                             | $A_{VLIM}$                            | (V <sub>DRL</sub> - V <sub>SFB</sub> )/V <sub>VLIM</sub>                          |                        | 2     |          | V/V   |

| VLIM_nSD Input Current (Cooling)               | I <sub>VLIMC</sub>                    | V <sub>OUT2</sub> < V <sub>REF</sub> /2                                           |                        | 0.1   | 1        | μΑ    |

| VLIM_nSD Input Current (Heating)               | $I_{VLIMH}$                           | V <sub>OUT2</sub> > V <sub>REF</sub> /2, sinking current                          | 8                      | 10    | 12       | μΑ    |

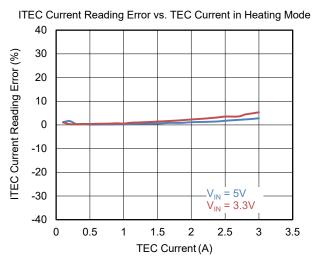

| TEC Current Measurement                        |                                       |                                                                                   |                        |       |          |       |

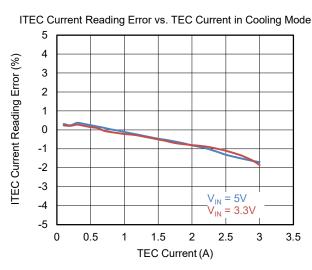

| Current Sense Gain                             | R <sub>CS</sub>                       |                                                                                   |                        | 0.285 |          | V/A   |

| Current Measurement Accuracy                   | I <sub>LDR_ERROR</sub>                | 1A ≤ I <sub>LDR</sub> ≤ 3A                                                        | -10                    |       | 10       | %     |

| ITEC Voltage Accuracy                          | V <sub>ITEC_AT_1_A</sub>              | Cooling, V <sub>REF</sub> /2 + I <sub>LDR</sub> × R <sub>CS</sub>                 | 1.493                  | 1.538 | 1.577    | V     |

| ITEC Bias Voltage                              | V <sub>ITEC_B</sub>                   | I <sub>LDR</sub> = 0A                                                             | 1.210                  | 1.250 | 1.285    | V     |

| Maximum ITEC Output Current                    | I <sub>ITEC</sub>                     |                                                                                   | -2                     |       | 2        | mA    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 2.7 \text{V to } 5.5 \text{V}, T_J = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ all typical values are measured at } T_J = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                    | SYMBOL                     | CONDITIONS                                                                     | MIN   | TYP   | MAX   | UNITS |

|------------------------------|----------------------------|--------------------------------------------------------------------------------|-------|-------|-------|-------|

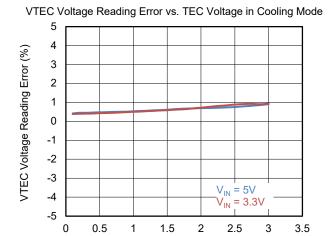

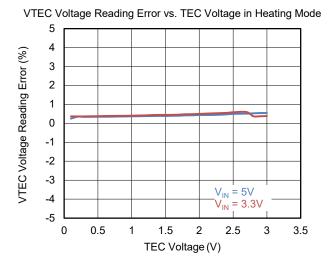

| TEC Voltage Measurement      |                            |                                                                                |       |       |       |       |

| Voltage Sense Gain           | A <sub>VTEC</sub>          |                                                                                | 0.24  | 0.25  | 0.26  | V/V   |

| Voltage Measurement Accuracy | V <sub>VTEC_AT_1.5_V</sub> | $V_{LDR} - V_{SFB} = 1.5V$ , $V_{REF}/2 + A_{VTEC} \times (V_{LDR} - V_{SFB})$ | 1.59  | 1.63  | 1.67  | V     |

| VTEC Bias Voltage            | $V_{VTEC\_B}$              | $V_{LDR} = V_{SFB}$                                                            | 1.225 | 1.250 | 1.285 | V     |

| Maximum VTEC Output Current  | R <sub>VTEC</sub>          |                                                                                | -2    |       | 2     | mA    |

| Temperature-Good             |                            |                                                                                |       |       |       |       |

| TMPGD Low Output Voltage     | $V_{TMPGD\_LO}$            | No load                                                                        |       |       | 0.4   | V     |

| TMPGD High Output Voltage    | $V_{TMPGD\_HO}$            | No load                                                                        | 2.0   |       |       | V     |

| TMPGD Low Output Impedance   | R <sub>TMPGD_LOW</sub>     |                                                                                |       | 50    |       | Ω     |

| TMPGD High Output Impedance  | R <sub>TMPGD_HIGH</sub>    |                                                                                |       | 80    |       | Ω     |

| High Threshold               | $V_{\text{OUT1\_THH}}$     | IN2N tied to OUT2, V <sub>IN2P</sub> = 1.5V                                    |       | 1.56  | 1.63  | V     |

| Low Threshold                | $V_{\text{OUT1\_THL}}$     | IN2N tied to OUT2, V <sub>IN2P</sub> = 1.5V                                    | 1.37  | 1.44  |       | V     |

| Internal Soft-Start          |                            |                                                                                |       |       |       |       |

| Soft-Start Time              | tss                        |                                                                                |       | 110   |       | ms    |

| VLIM_nSD Shutdown            |                            |                                                                                |       |       |       |       |

| Low Voltage Threshold        | $V_{VLIM\_nSD\_THL}$       |                                                                                |       |       | 0.07  | V     |

| Thermal Shutdown             |                            |                                                                                |       |       |       |       |

| Threshold                    | T <sub>SHDN_TH</sub>       |                                                                                |       | 170   |       | °C    |

| Hysteresis                   | T <sub>SHDN_HYS</sub>      |                                                                                |       | 30    |       | °C    |

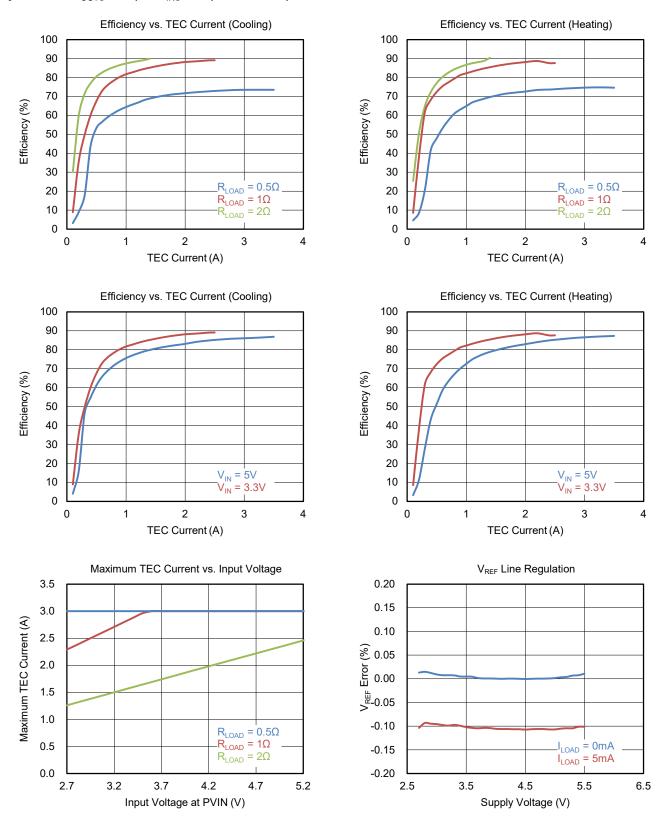

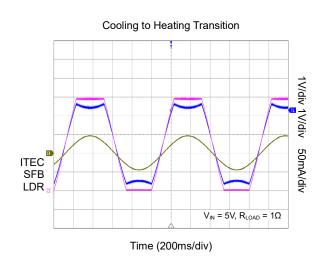

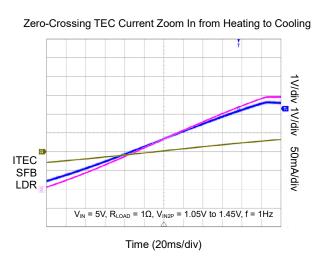

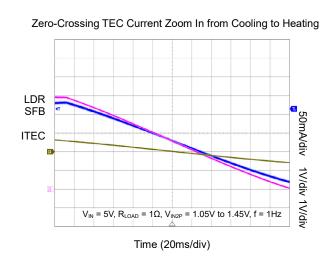

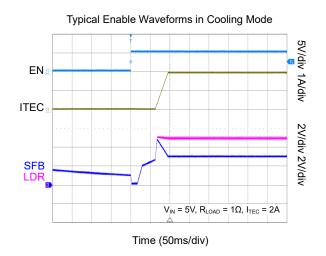

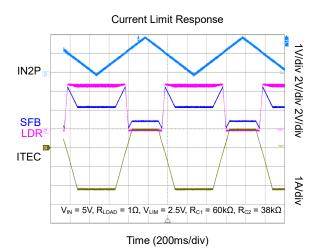

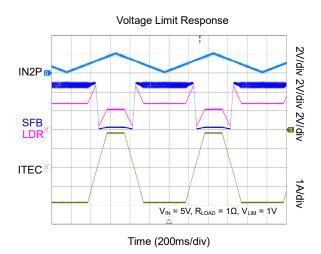

#### TYPICAL PERFORMANCE CHARACTERISTICS

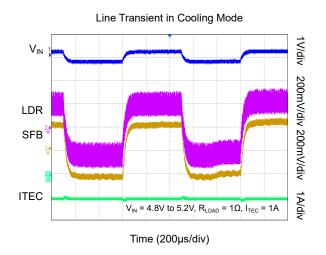

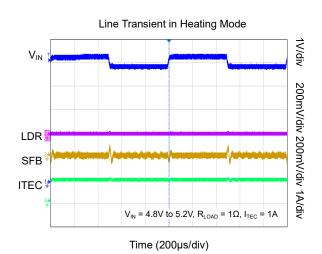

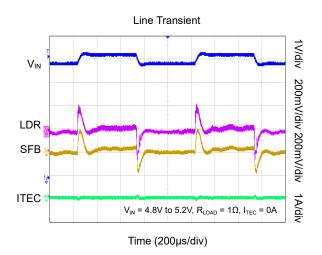

$T_J$  = +25°C,  $C_{OUTS}$  = 10 $\mu$ F,  $C_{INS}$  = 10 $\mu$ F and L = 1 $\mu$ H, unless otherwise noted.

$T_J$  = +25°C,  $C_{OUTS}$  = 10 $\mu$ F,  $C_{INS}$  = 10 $\mu$ F and L = 1 $\mu$ H, unless otherwise noted.

$T_J$  = +25°C,  $C_{OUTS}$  = 10 $\mu$ F,  $C_{INS}$  = 10 $\mu$ F and L = 1 $\mu$ H, unless otherwise noted.

TEC Voltage (V)

$T_J$  = +25°C,  $C_{OUTS}$  = 10 $\mu$ F,  $C_{INS}$  = 10 $\mu$ F and L = 1 $\mu$ H, unless otherwise noted.

$T_J$  = +25°C,  $C_{OUTS}$  = 10 $\mu$ F,  $C_{INS}$  = 10 $\mu$ F and L = 1 $\mu$ H, unless otherwise noted.

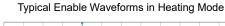

Time (50ms/div)

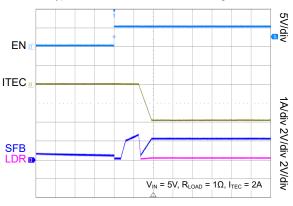

Typical Switch and Voltage Ripple Waveforms in Cooling Mode

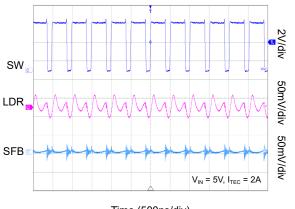

Typical Switch and Voltage Ripple Waveforms in Heating Mode

Time (500ns/div)

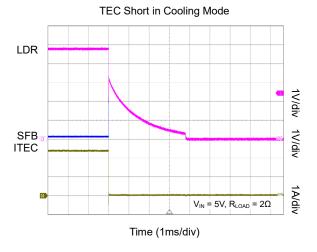

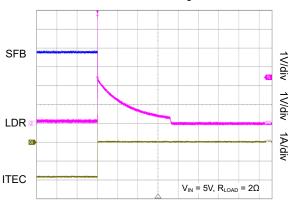

TEC Short in Heating Mode

Time (1ms/div)

$T_J$  = +25°C,  $C_{OUTS}$  = 10 $\mu$ F,  $C_{INS}$  = 10 $\mu$ F and L = 1 $\mu$ H, unless otherwise noted.

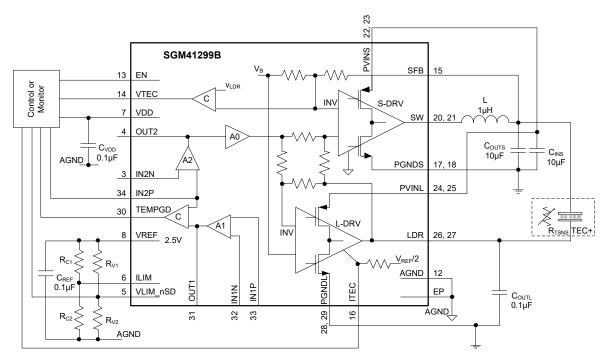

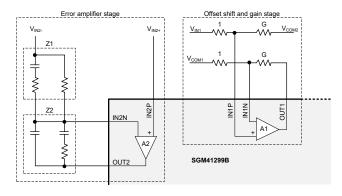

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Block Diagram

#### **OPERATION PRINCIPLE AND APPLICATION**

The SGM41299B contains all the necessary circuits to make a full analog control loop for a TEC thermostat, including precision chopper amplifiers, TEC differential driver and reference voltage plus monitoring and limiting functions and protections for over-temperature and over-current (see Figure 1).

The differential driver has two arms: a linear arm with high transfer gain and a switching regulator arm with a relatively lower gain. With this structure, the precise but inefficient linear driver saturates at low differential output swing such that in most of the output range only the switching arm is effectively regulating the output. This keeps the overall driving efficiency very high and close to a common switching converter rather than a linear amplifier.

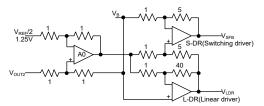

Figure 2 shows a model for the differential driver. The  $V_{REF}/2 = 1.25V$  is the common mode signal reference (zero) for the amplifiers. From the A0 input which is OUT2 from the compensator to the LDR output, the transfer ratio ( $V_{OUT2}$ -1.25 to  $V_{LDR}$ - $V_{B}$ ) is designed to be a 40× gain. The switching arm is designed to amplify the divider output (1/5 of the  $V_{LDR}$ - $V_{B}$ ) by 5× and 5/6 of  $V_{OUT2}$ -1.25 by 6× gain. Overall, it makes the differential output to follow 5 × ( $V_{OUT2}$ -1.25). Refer to the transfer plots in the typical performance characteristics for details.

Figure 2. The Single-ended  $V_{\text{OUT2}}$  to Differential Output Transfer Model

The output current and voltage limits are independently set with programming resistor dividers (powered from  $V_{REF}$ ) for both driving directions (sink and source). The bias currents can be different in each direction. This programming flexibility allows the operation range to be set for a wide range of TEC specifications.

#### **Soft-Start**

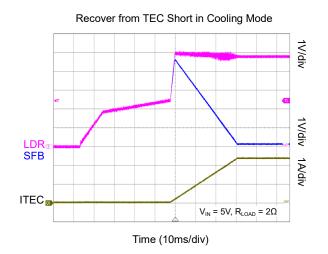

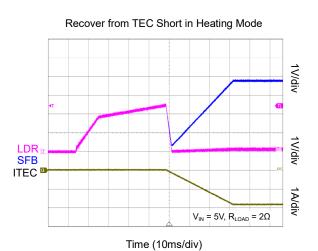

When the device starts to operate or resumes from the over-temperature or switch over-current protection conditions, both arms (the LDR and switching) output initially go to 0V and then ramp up to the common voltage of  $V_B$  (no differential driving at this moment) and then they start to split and the differential driving starts. Refer to the waveform captures in the typical performance characteristics for details. Before the differential outputs raise off the ground level enough, the internal cooling/heating current detection is not certain and the internal bias currents to VLIM and ILIM may toggle correspondingly.

#### **Over-Voltage Protection**

SGM41299B has an input over-voltage protection (OVP) to protect the device. When the  $V_{DD}$  voltage of the SGM41299B exceeds the OVP threshold of 5.75V, the device stops switching.

#### **TEC Thermostat Basis**

The TEC device is made of semiconductor ( $Bi_2Te_3$ ) thermo-electric piles that have positive or negative mobility potentials in the P-doping or N-doping, in which the mobile charge is hotter or cooler than the bulk. When foreign chargers compensate the chargers of hot or cool spots, mobile chargers are released in even hotter or cooler spots and the procedure makes the bulk hotter or cooler.

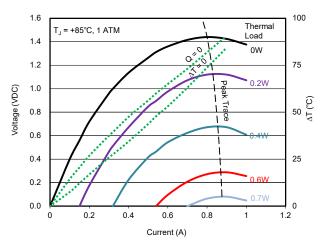

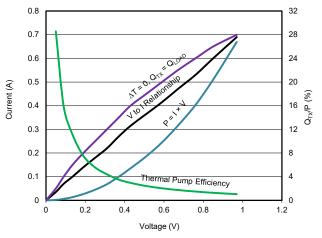

Figure 3 shows the Voltage-Current (I-V) plots of a typical 9-coupler TEC sample at different thermal power transfer values when acting as a cooler. Derived from this figure, the thermal pumping efficiency is given in Figure 4 and the resistive loss to the leakage loss relationship is extracted and given in Figure 5. The Q = 0 curve shows the I-V points with the largest generated  $\Delta T$  across TEC. The  $\Delta T$  = 0 curve gives the I-V points with the highest heat transfer (thermal flux). The peak trace shows the maximum achievable  $\Delta T$  for different thermal loads (heat transfer). After the peak trace and at higher currents the driver voltage to  $\Delta T$  gain polarity is reversed so the cooling current must be carefully limited below the peak trace to maintain a monotonic relation between drive current and generated ΔT. This is essential for the stability and loop convergent.

Figure 3. The Typical I-V and Thermal Transfer Plot

Figure 4. Thermal Pump Efficiency. The  $Q_{TX}/P$  is the Ratio of Transferred Heat to the Driving Power (in %)

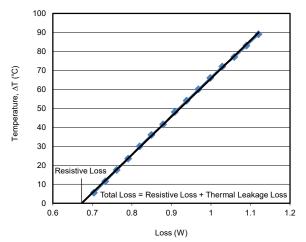

Figure 5. Resistive Loss and Thermal Leakage

From Figure 4 it can be concluded that a larger capacity TEC (capable for higher heat power transfer) has a better efficiency at the same heat load. Figure 5 illustrates that the TEC resistive loss ( $P = V \times I$ ) is bigger than leakage loss that is due to the natural heat transfer (leakage) through the thermal resistance of the TEC from the hot side to the cool side. The resistive loss is the dominant portion of the total loss.

Figure 6. The Maximum and Suitable (Below Marginal)

Operating Ranges

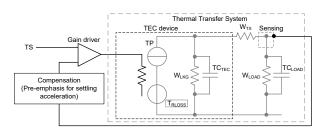

Figure 7. TEC Thermostat Combined Loop Model

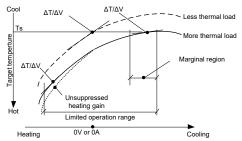

Figure 6 shows that the  $\Delta T/\Delta V$  (differential gain of drive voltage to temperature difference) varies in the operation range and is smaller at higher thermal loads.

Figure 7 shows the closed loop model of a TEC thermostat with its dual major poles and other key elements in the thermal system. The load thermal capacitance  $TC_{\text{LOAD}}$  (heat capacity) and the heat transfer loss  $W_{\text{TX}}$  along with the TEC thermal capacitance (TC $_{\text{TEC}}$ ) results in a  $2^{\text{nd}}$  order system for control loop to compensate. The TP stands for power of the thermal pump and  $T_{\text{RLOSS}}$  models the thermal leakage loss.

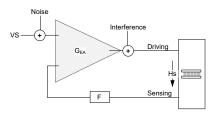

Figure 8. Error Sources in a TEC Thermostat

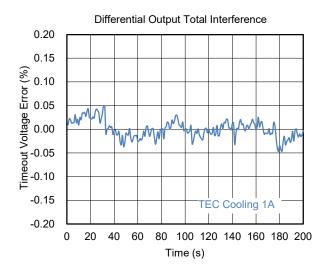

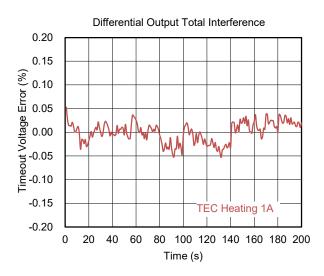

Based on the system model shown in Figure 8, if the temperature set point is VS, the deterministic temperature error  $T_{DE}$  and the sensed temperature  $T_{SNS}$  can be represented as:

$$T_{DE} = \frac{\text{Noise}}{F} + \frac{\text{Hs}}{1 + F \times \text{Hs} \times G_{EA}} \times \text{Interference}$$

(1)

$$T_{SNS} = \frac{VS}{F} \times \frac{G_{EA} \times Hs}{1 + G_{EA} \times Hs \times F} + T_{DE}$$

(2)

For the total interference value of the device, please refer to the SGM41299B typical performance characteristics table.

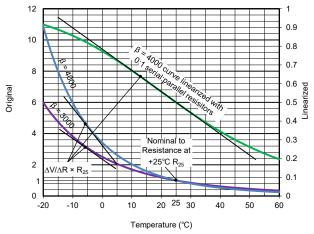

Figure 9. Typical NTC Responsivity and Linearization

#### **TEC Thermostat Design**

Several types of temperature sensors such as NTC, thermo-resistance (PTR), PN junction and thermocouples <sup>1</sup> can be used for sensing the temperature of the object to make a thermostat. The NTC without linearization has typically the largest responsivity in the cooling range and is suitable for TEC applications in the cooling mode.

For example, a typical PN junction type sensor has a responsivity of about -2mV/°C. A 1k $\Omega$  NTC with  $\beta$  = 3000 and 200 $\mu$ A bias has almost the same responsivity at 60°C. Such responsivity is good enough for most of the thermostat applications; the main design constrain is usually the transfer gain of the TEC device. The sensor system noise, settling time and system pull-in time are the 3 main challenges for a stable design. The thermal system noise impact can be mitigated by using a low noise sensor, using a stable driver or by increasing the load thermal capacity. The response

Fast pull-in time is desired for quick calibration in production or for a quick set-up in a specific application. An error-adaptive gain (more gain when error is large and less gain when it is small) helps getting a calibration-free and fast pull-in performance for the loop. Having a digital segmented loop that has different loop gains for different error amplitude is more convenient for flexible parameter programming and achieving larger time constants.

Table 1. Factors to Consider in TEC Thermostat Design

| Items                    | Description                                                                                                                                                                                                                                                       |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ambient                  | Design objective. The maximum temperature at                                                                                                                                                                                                                      |

| Temperature              | which the thermostat can work.                                                                                                                                                                                                                                    |

| Thermal Load             | Design objective. The load and its transient condition, i.e., the power of the thermal load and how fast the load power changes in operation.                                                                                                                     |

| Control<br>Range         | Design objective. The temperature to maintain and its accuracy, resolution and its range.                                                                                                                                                                         |

| Response<br>Time         | Design objective. The response time when the system is locked-in with limited ambient temperature interference sudden change.                                                                                                                                     |

| Pull-In Time             | Design objective. The time to pull the system in the locked-in status from the uncontrolled (loss of control) status during start-up or after pull-off by a heavy interference.                                                                                   |

| TEC<br>Performance       | Constrain condition verification. To evaluate or select a TEC device for its maximum cooling gain (at the highest available control temperature and maximum thermal load) and heating gain (at the lowest available control temperature and lowest thermal load). |

| Sensor<br>Performance    | Constrain condition verification, i.e., its worst responsivity in desired range. The key element affecting the thermostat performance.                                                                                                                            |

| Thermal Bias             | Ambient impact, i.e., the bias power in the given ambient temperature range: TEC/object to ambient thermal coupling, a constrain condition for characterize in system.                                                                                            |

| Driving<br>Response      | The system characterization. The cooling gain and heating gain at segmented different TEC loading condition.                                                                                                                                                      |

| Injection<br>Response    | The system characterization, on both the thermal load injection response and thermal bias (ambient) injection.                                                                                                                                                    |

| System Noise             | The actual/simulated system characterization.                                                                                                                                                                                                                     |

| Loop Gain /<br>Bandwidth | Design synthesis, derived from the objectives and conditions, match with the sensor performance.                                                                                                                                                                  |

| Loop Noise               | Design synthesis, derived from the objectives and conditions.                                                                                                                                                                                                     |

| Control Mode             | Design synthesis, derived from the objectives and conditions.                                                                                                                                                                                                     |

NTC is negative temperature co-efficiency resistor; PTR is positive temperature co-efficiency resistor like platinum film; junction voltage is the PN junction forward voltage bias with a constant current. The junction voltage type and thermal coupling may be easier to fabricate for integration.

DECEMBER 2020

time of a thermal system can also be improved by a pre-emphasizer stage. A digital PID compensator with the adaptive gain can be used instead of the analog one. This is better for design flexibility as it can easily fit different conditions.

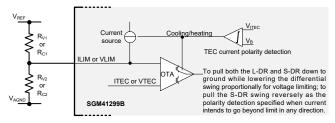

#### **Programming the Limits**

Both current limit and voltage limit are set by similar internal circuits. Current and voltage limit points are sent to an operational trans-impedance amplifier with current sinking and or sourcing capability. If the limits are reached, the switching arm output magnitude is reduced or is cut off to prevent damages.

Figure 10. Voltage and Current Limit Circuit Architecture

As shown in Figure 10, the external resistor dividers (for voltage and current individually) for limit settings are biased with two current sinking/pouring sources. When the current polarity changes, the two bias current sources are turned on or off and inject into the resistor dividers, the voltages at VLIM or ILIM are set high or low to 1.25V, which is the corresponding value for both zero driving current and zero differential driving voltage. One bias current pours  $I_{ILIMC}$  (40µA) off the ILIM when driving is detected as in cooling direction and the other sinks  $I_{ILIMH}$  (10µA) into the VLIM when driving in heating direction. The 4 divider resistances are calculated from the following equations:

$$R_{V1} = 2.5 \times 10^5 \times \left(1 - \frac{V_{TEC\_MAX\_HEATING}}{V_{TEC\_MAX\_COOLING}}\right)$$

(3)

$$R_{V2} = R_{V1} / \left(\frac{5}{V_{TEC\_MAX\_COOLING}} - 1\right)$$

(4)

$$R_{C1} = 6.25 \times 10^4 \times \left( \frac{1.25 + 0.285 \times I_{TEC\_MAX\_COOLING}}{1.25 - 0.285 \times I_{TEC\_MAX\_HEATING}} - 1 \right) (5)$$

$$R_{C2} = R_{C1} / \left( \frac{2.5}{1.25 - 0.285 \times I_{TEC\_MAX\_HEATING}} - 1 \right)$$

(6)

The  $V_{\text{TEC\_MAX\_HEATING}}$ ,  $V_{\text{TEC\_MAX\_COOLING}}$ ,  $I_{\text{TEC\_MAX\_HEATING}}$  and  $I_{\text{TEC\_MAX\_COOLING}}$  are parameters given for specific TEC device as listed maximum voltages and currents in its specification. The limiting voltage for either ILIM or VLIM in either cooling or heating should be kept away from 1.25V farer enough, which is more than 50mV, to

avoid unstable caused by impaired limiting direction when the setting current or voltage swing is too close to zero.

#### **Output Monitoring and Reference Voltage**

The differential output voltage and bidirectional output current are converted into single ended output signals (biased to  $V_{REF}/2$  = 1.25V) for external monitoring ( $V_{TEC}$  and  $I_{TEC}$  output voltages). The characteristic parameters of these monitoring outputs and the reference voltage ( $V_{REF}$ , which is used for biasing external sensing networks) and the temperature-good signal are given in the SGM41299B electrical characteristics table.

#### **Designing the Analog Loop**

A1 is a chopper amplifier designed for temperature sensor signal conditioning (such as changing its polarity, adjusting the offset or increasing its sensitivity). The chopper amplifier A2 is designed for making an error amplifier that provides gain and compensation to either an external control input or to the output of the chopper amplifier A1.

Figure 11. Using SGM41299B Amplifiers

Figure 11 shows an applicable circuit in which A2 is used to make an error amplifier with external compensation network Z1 and Z2, and A1 is used to make a gain (G) stage with level shifting from  $V_{\text{COM1}}$  at input side to  $V_{\text{COM2}}$  at output (OUT1). The temperature setting can be fed into either  $V_{\text{IN2+}}$  or  $V_{\text{IN2-}}$  and the temperature sensor (for example NTC) can replace one of the four resistors.

#### Operate as Driver in a Digital Loop

When the device is used in a digital thermostat loop, it works as a single-ended to differential power amplifier with programmable current limiting and voltage limiting. The single-ended input to the power stage is the OUT2 that is output of A2, which is centered to 1.25V and the differential swing is centered at 1.5V for  $V_{DD} < 4V$  or 2.5V for  $V_{DD} > 4V$ . The external input to the power amplifier should be applied through any of the amplifier input and then the A2 transfers to OUT2 for the power amplifier.

Either the voltage limiting or the current limiting is performed with a single amplifier for two directional limiting thresholds separately. The limiting directions and thresholds follow the change of and match with the actual TEC driving polarity autonomously with the internal TEC current detection circuit. The mechanism of following has to be maintained is using DACs to programming the thresholds, which could be implemented by insertion of serial resistor between the DAC output to the VLIM or ILIM that enables the bias current changing the threshold matching the TEC driving polarity. Each threshold should sit aside 1.25V farer then 50mV minimally.

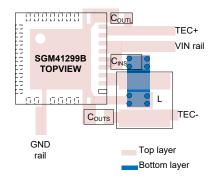

#### **Layout and Component Selection**

The PWM chopper and the L and C components need to be carefully placed and routed. Keep the key components (L,  $C_{INS}$ ,  $C_{OUTS}$  and  $C_{OUTL}$ ) close to the device and separate the high current and reference grounds and connect them in one point. Keep the switching current loop area as small as possible. Choose proper L,  $C_{INS}$ ,  $C_{OUTS}$  and  $C_{OUTL}$  for operating frequency and currents and choose a low DCR inductor and low ESR capacitors.

Figure 12. Key Components Placement and Layout

**Table 2. Recommended Inductor and Capacitors**

| Designation       | Vendor           | Device No.                 | Value | Verified Suitable Range |

|-------------------|------------------|----------------------------|-------|-------------------------|

| L                 | Würth-Elektronik | 74439344010                | 1µH   | 0.68μH ~ 1.5μH          |

| C <sub>INS</sub>  | Murata           | C426637/GRJ31CR71E106KE11L | 10µF  | ≥ 10µF                  |

| C <sub>OUTS</sub> | Murata           | C426637/GRJ31CR71E106KE11L | 10µF  | 10μF ~ 22μF             |

| C <sub>OUTL</sub> | Murata           | 0805B104K500NT             | 0.1µF | 0.1μF ~ 1μF             |

#### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Page

Changed from product preview to production data.....

....All

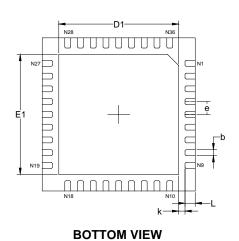

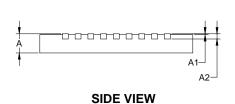

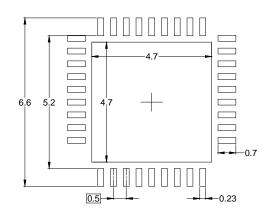

# PACKAGE OUTLINE DIMENSIONS TQFN-6×6-36L

RECOMMENDED LAND PATTERN (Unit: mm)

| Cymphol | Dimensions In Millimeters |             |      |  |  |  |

|---------|---------------------------|-------------|------|--|--|--|

| Symbol  | MIN                       | MOD         | MAX  |  |  |  |

| А       | 0.7                       | 0.75        | 0.8  |  |  |  |

| A1      | 0                         | 0.02        | 0.05 |  |  |  |

| A2      |                           | 0.203 REF   |      |  |  |  |

| b       | 0.18                      | 0.28        |      |  |  |  |

| D       | 6 BSC                     |             |      |  |  |  |

| Е       |                           | 6 BSC       |      |  |  |  |

| D1      | 4.6                       | 4.6 4.7 4.8 |      |  |  |  |

| E1      | 4.6                       | 4.6 4.7 4.8 |      |  |  |  |

| L       | 0.35 0.4 0.45             |             |      |  |  |  |

| е       | 0.5 BSC                   |             |      |  |  |  |

| k       | 0.25 REF                  |             |      |  |  |  |

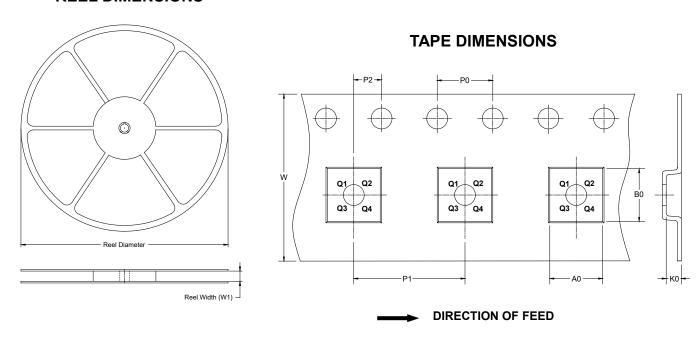

#### TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TQFN-6×6-36L | 13"              | 16.4                     | 6.40       | 6.40       | 1.40       | 4.0        | 8.0        | 2.0        | 16.0      | Q1               |

TX10000.000

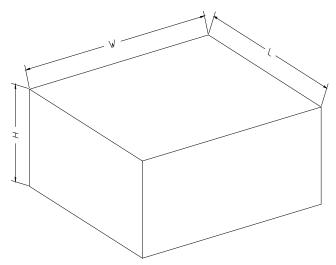

#### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-----------|----------------|---------------|----------------|--------------|

| 13″       | 386            | 280           | 370            | 5            |