# **General Description**

The SY6974 is a fully-integrated switching battery charger with system power path management devices for single cell Li-ion and Li-polymer battery in a wide range of tablet and other portable devices. Its low impedance power path optimizes switching conversion efficiency, reduces battery charging time and extends battery life during the discharging mode. The I<sup>2</sup>C serial interface with charging and system settings makes the device a truly flexible solution.

The device supports a wide range of input sources, including standard USB port and high power DC adapter. The SY6974 takes the result from detection circuit in the system, such as USB PHY device. The SY6974 meets USB On-the-Go operation power rating specification by supplying 5.15V (programmable) on BUS with current limit up to 1.2A (programmable).

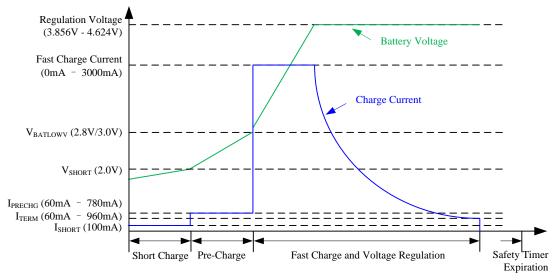

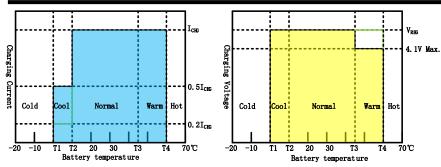

The power path management regulates the system voltage slightly above battery voltage but does not drop below 3.5V minimum system voltage (programmable). With this feature, the switching converter will keep working to support the system load even when the battery is completely depleted or removed. When the input current limit or voltage limit is reached, the power path management will reduce the charging current to zero firstly. If the system load continues to increase, the power path will discharge the battery to provide the power required by system. This supplement mode operation prevents overloading the input source. The device initiates and completes a charging cycle without software control. It automatically detects the battery voltage and charges the battery in five phases: battery short, preconditioning, constant current and constant voltage and top-off charging (optional). At the end of the charging cycle, the charger automatically will terminate when the charge current is below a preset limit in the constant voltage phase. When the full battery falls below the recharge threshold, the charger will automatically start another charging cycle. The SY6974 can be compliant with JEITA spec for the 4.2V Li-ion battery.

The device provides various safety features for battery charging and system operation, including negative thermistor monitoring, charging safety timer and over-voltage / over-current protections. The thermal regulation will reduce charge current when the junction temperature exceeds  $110 \,^{\circ}$ C (programmable).

The STAT output reports the charging status and any fault conditions. The /PG output in the SY6974 indicates if a good power source is present. The INT immediately will notify the host when a fault occurs.

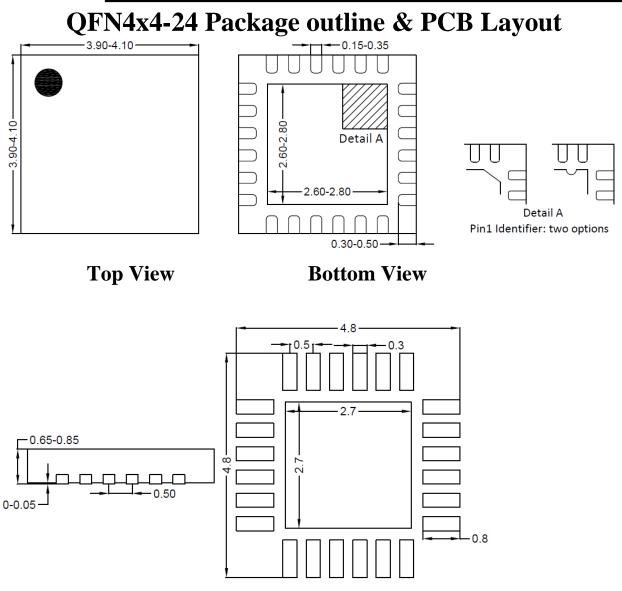

The SY6974 are available in QFN4x4-24 package.

# **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY6974QCC       | QFN4x4-24    |      |

# Features

- High Efficiency 3A 1.5MHz Buck Mode Charger

- Support 3.9V-13.5V Input Voltage Range

- Programmable IDPM/VDPM to Support the USB and Adapter

- 3.856V-4.624V Adjustable Charge Voltage

- Support Narrow VDC Power Path Management

- JEITA Compliance

- ±0.5% Charge Voltage Regulation

- Charge Status Outputs for LED or Host Processor

- Maximum 1.2A 1.5MHz Boost OTG Current

- 4.85V-5.3V Adjustable OTG Output Voltage

- Selectable OTG Output Current Limit

- $-\pm 1.5\%$  Output Regulation in Boost Mode

- Soft-Start up to 500 µF Capacitive Load

- Constant Current (CC) Limit

- Full BATFET Control to Support Shipping Mode, Wake up, and System Reset

- Safety

- Battery Temperature Sensing for Charge and Boost Mode

- Battery Charging Safety Timer

- Thermal Regulation and Thermal Shutdown

- Input/System over-Voltage Protection

- MOSFET over-Current Protection

- Low Battery Leakage Current and Support Shipping Mode

- 4mm x 4mm QFN-24 Package

# Applications

- Smart Phone

- Tablet PC

- Power Bank

- Portable Internet Devices

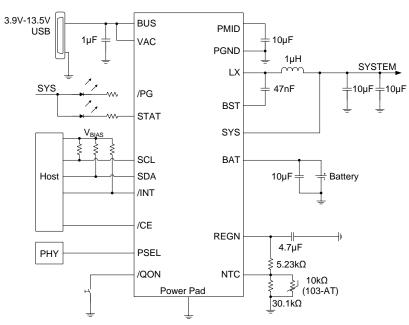

#### Figure 1. Schematic Diagram

# **Typical Application**

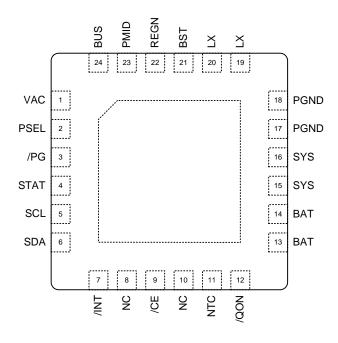

# Pinout

(QFN4x4-24)

Top Mark: CUExyz(device code: CUE, x=year code, y=week code, z= lot number code)

| Pin Name | Pin No | Pin Description                                                                                                                                                                                                                                                                       |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAC      | 1      | Charge input voltage sense. This pin must be connected close to BUS pin.                                                                                                                                                                                                              |

| PSEL     | 2      | Power source selection input. High indicates a USB host source and Low indicates an adapter source. In default mode, set 500mA input current limit by pulling this pin high and set 2.4A input current limit by pulling this pin low.                                                 |

| /PG      | 3      | Open drain active low power good indicator. Connect to the pull up rail via $10k\Omega$ resistor. Low indicates a good input source.                                                                                                                                                  |

| STAT     | 4      | Open drain charge status output to indicate various charger operation. Connect to the pull up rail via $10k\Omega$ resistor. Low indicates charge in progress. High indicates charge complete or charge disabled. When any charge fault condition occurs, STAT pin will blink at 1Hz. |

|          |        | The STAT pin function can be disabled when STAT_DIS bit is set.                                                                                                                                                                                                                       |

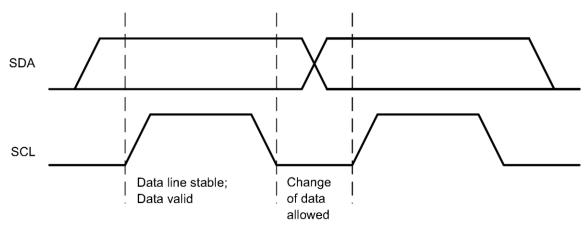

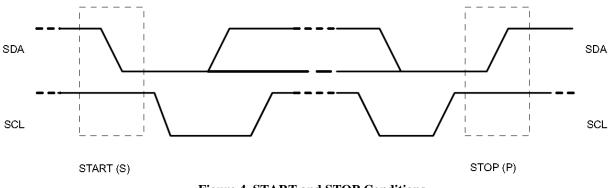

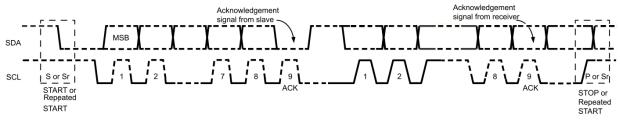

| SCL      | 5      | I <sup>2</sup> C Interface clock. Connect SCL to the logic rail through a $10k\Omega$ resistor.                                                                                                                                                                                       |

| SDA      | 6      | I <sup>2</sup> C Interface data. Connect SDA to the logic rail through a $10k\Omega$ resistor.                                                                                                                                                                                        |

| /INT     | 7      | Open-drain interrupt output. Connect the /INT to a logic rail via $10k\Omega$ resistor. The /INT pin sends active low, 256µs pulse to host to report charger device status and fault.                                                                                                 |

| NC       | 8, 10  | No connect.                                                                                                                                                                                                                                                                           |

| /CE      | 9      | Active low charge enable pin. Battery charging will be enabled when REG01[4]=1 and /CE pin =Low. /CE pin must be pulled high or low.                                                                                                                                                  |

| NTC      | 11     | Connect a resistor divider from REGN to NTC to GND to achieve battery thermal protection. Charge will suspend when NTC pin is out of range.<br>Recommend 103AT-2 thermistor.                                                                                                          |

|             | 1     |                                                                                                                                                                                                                       |

|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |       | BATFET enable control in shipping mode and BATFET reset function.                                                                                                                                                     |

| /QON        | 12    | When BATFET is in shipping mode, logic high to low transition on this pin with minimum of $T_{QON\_LOW}$ low level will turn on BATFET to exit shipping mode. This pin is internally pulled up to default high logic. |

|             |       | When BUS is not plugged in and BATFET_DIS=0, a logic low of $T_{QON_RST}$ will reset SYS (system power) by turning BATFET off for $T_{BATFET_RST}$ and then re-enable BATFET.                                         |

| BAT         | 13,14 | Battery connection point to the positive terminal of the battery pack. The internal BATFET is connected between BAT and SYS. Connect a $10\mu$ F closely to the BAT pin                                               |

| SYS         | 15,16 | System connection point. The internal BATFET is connected between BAT and SYS. When the battery falls below the minimum system voltages, switch mode converter will keep SYS above the minimum system voltage.        |

| PGND        | 17,18 | Power ground connection node. Internally, PGND is connected to the source of the n-<br>channel LSFET. On PCB layout, connect directly to ground connection of input and<br>output capacitors of the charger.          |

| LX          | 19,20 | Switching node pin. Connect to external inductor.                                                                                                                                                                     |

| BST         | 21    | HSFET driver positive supply. Connect a 47nF bootstrap capacitor from LX to BST.                                                                                                                                      |

| REGN        | 22    | LSFET driver positive supply. Connect a $4.7\mu$ F ceramic capacitor from REGN to analog GND. The capacitor should be placed close to the IC. REGN also serves as bias rail of NTC pin.                               |

| PMID        | 23    | Connected to the drain of the reverse blocking MOSFET and the drain of HSFET. Put at least 10µF on PMID to PGND, and place it as close as possible to IC.                                                             |

| BUS         | 24    | Charger power input pin. Place a $1\mu$ F ceramic capacitor from BUS to PGND and place it as close as possible to IC.                                                                                                 |

| Exposed pad | -     | Exposed pad beneath the IC for heat dissipation. Always solder exposed pad to the board, and have vias on the Power Pad plane star-connecting to PGND and ground plane for high current power converter.              |

# Absolute Maximum Ratings (Note 1)

| BUS, VAC, PMID, LX                   |             |

|--------------------------------------|-------------|

| Package Thermal Resistance (Notes 2) |             |

| heta JA                              |             |

| θ <sub>JC</sub> (top)                |             |

| θ յв                                 |             |

| $\psi$ <sup>JT</sup>                 | 0.35 °C/W   |

| Junction Temperature Range           | ℃ to +150 ℃ |

| Operating Temperature Range          | ℃ to +150 ℃ |

| Storage Temperature                  | ℃ to +150 ℃ |

| Lead Temperature (Soldering, 10s)    | +300 ℃      |

|                                      |             |

| ESD Susceptibility                   |             |

|                                      |             |

| HBM (Human Body Mode)     | 2kV  |

|---------------------------|------|

| CDM (Charged Device Mode) | 200V |

# Recommended Operating Conditions (Note 3)

| BUS, VAC, PMID, LX 0V to +16V                                                       |

|-------------------------------------------------------------------------------------|

| BAT, SYS, REGN, PSEL, /PG, STAT, SCL, SDA, /INT, /CE, NTC, /QON, BST-LX 0V to +5.5V |

| Junction Temperature Range                                                          |

| Ambient Temperature Range                                                           |

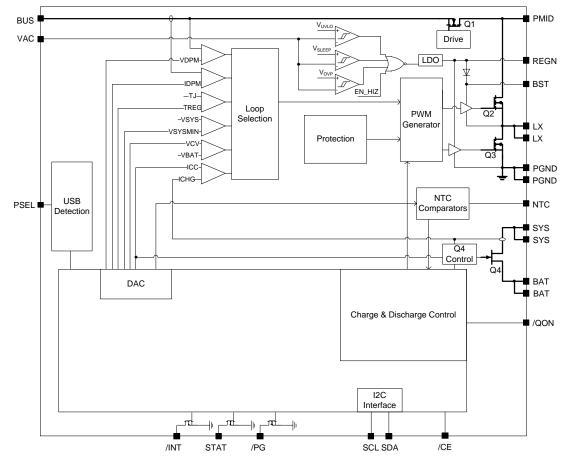

# **Block Diagram**

Figure 2. Block Diagram

# **Electrical Characteristics**

$(V_{BUS\_UVLOZ} < V_{BUS} < V_{ACOV} and V_{BUS} > V_{BAT} + V_{SLEEPZ}, T_J = 25$ °C for typical values unless otherwise noted.)

| Parameter                                          | Symbol               | Test Conditions                                                                                                                                          | Min  | Тур        | Max         | Unit   |

|----------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|-------------|--------|

| Quiescent Currents                                 |                      |                                                                                                                                                          |      |            |             |        |

|                                                    |                      | VBUS <vbus_uvloz, v,<br="" vbat="4.5">leakage between BAT and BUS</vbus_uvloz,>                                                                          |      |            | 5           | μΑ     |

| Battery Discharge Current (BAT)                    | I <sub>BAT</sub>     | V <sub>BAT</sub> =4.5 V, High-Z Mode, no<br>BUS, BATFET disabled                                                                                         |      | 15         | 25          | μΑ     |

|                                                    |                      | V <sub>BAT</sub> =4.5 V, High-Z Mode, no<br>BUS, BATFET enabled                                                                                          |      | 40         | 55          | μΑ     |

| Input Supply Current in High-Z                     | I <sub>BUS</sub> HIZ | V <sub>BUS</sub> =5V, no battery, High-Z<br>mode enabled                                                                                                 |      | 20         | 35          | μΑ     |

| Mode                                               | IBUS_HIZ             | V <sub>BUS</sub> =12V, no battery, High-Z<br>mode enabled                                                                                                |      | 25         | 50          | μΑ     |

|                                                    |                      | VBUS>VBUS_UVLOZ, VBUS>VBAT,<br>converter not switching                                                                                                   |      | 1.5        | 3           | mA     |

| Input Supply Current (BUS)                         | I <sub>BUS</sub>     | V <sub>BUS</sub> > V <sub>BUS_UVLOZ</sub> , V <sub>BUS</sub> >V <sub>BAT</sub> ,<br>converter switching, V <sub>BAT</sub> =3.8V,<br>I <sub>SYS</sub> =0A |      | 3          |             | mA     |

| Battery Discharge Current in Boost<br>Mode         | Iotgboost            | V <sub>BAT</sub> =4.2V, Boost mode,<br>I <sub>BUS</sub> =0A, converter switching                                                                         |      | 3.5        |             | mA     |

| BUS/BAT Power up                                   |                      |                                                                                                                                                          |      |            |             |        |

| BUS Operating Range                                | V <sub>BUS_OP</sub>  |                                                                                                                                                          | 3.9  |            | 13.5        | V      |

| BUS for Active IC and I <sup>2</sup> C, no Battery | VBUS_UVLOZ           | Rising value to active I <sup>2</sup> C<br>Falling value                                                                                                 |      | 3.3<br>2.9 | 3.5<br>3.25 | V<br>V |

| Sleep Mode Falling Threshold                       | VSLEEP               | VBUS falling, VBUS-VBAT                                                                                                                                  | 25   | 65         | 120         | mV     |

| Sleep Mode Rising Threshold                        | VSLEEPZ              | V <sub>BUS</sub> rising, V <sub>BUS</sub> -V <sub>BAT</sub>                                                                                              | 170  | 250        | 300         | mV     |

| BUS over-Voltage Rising Threshold                  | VACOV                | V <sub>BUS</sub> rising, REG06[7:6]=00                                                                                                                   | 5.7  | 5.9        | 6.1         | v      |

| BUS over-Voltage Recovery<br>Threshold             | VACOV_RC             | V <sub>BUS</sub> falling, REG06[7:6]=00                                                                                                                  | 5.5  | 5.7        | 5.9         | V      |

| BUS over-Voltage Rising Threshold                  | VACOV                | V <sub>BUS</sub> rising, REG06[7:6]=11                                                                                                                   | 13.8 | 14.1       | 14.4        | V      |

| BUS over-Voltage Recovery<br>Threshold             | VACOV_RC             | V <sub>BUS</sub> falling, REG06[7:6]=11                                                                                                                  | 13.5 | 13.8       | 14.1        | V      |

| Dettern for Active PC as DUC                       | N/                   | $V_{BAT}$ rising value to active I <sup>2</sup> C                                                                                                        |      | 2.1        | 2.3         | V      |

| Battery for Active I <sup>2</sup> C, no BUS        | VBAT_UVLOZ           | V <sub>BAT</sub> falling                                                                                                                                 |      | 1.8        | 2.0         | V      |

| Battery Depletion Threshold                        | VBAT_DPL             | V <sub>BAT</sub> falling                                                                                                                                 | 2.15 | 2.3        | 2.5         | V      |

| Battery Depletion Recovery<br>Threshold            | VBAT_DPLZ            | V <sub>BAT</sub> rising                                                                                                                                  | 2.3  | 2.55       | 2.7         | v      |

| Bad Adapter Detection Threshold                    | V <sub>BUSMIN</sub>  | V <sub>BUS</sub> falling                                                                                                                                 | 3.6  | 3.7        | 3.8         | V      |

| Bad Adapter Detection Hysteresis                   | VBUSMIN_HYST         | V <sub>BUS</sub> rising                                                                                                                                  |      | 100        |             | mV     |

| Bad Adapter Detection Current Source               | Ibadsrc              |                                                                                                                                                          |      | 30         |             | mA     |

| Bad Source Detection Duration                      | <b>t</b> BADSRC      |                                                                                                                                                          |      | 30         |             | ms     |

| Power Path Management                              |                      |                                                                                                                                                          |      |            |             |        |

| System Regulation Voltage                          | V <sub>SYS_MAX</sub> | Isys = 0A, V <sub>BAT</sub> >V <sub>SYSMIN</sub> ,<br>BATFET off, V <sub>BAT</sub> up to 4.35V,<br>V <sub>SYS</sub> =V <sub>BAT</sub> +50mV              | 4.35 | 4.4        | 4.43        | v      |

| System Regulation Voltage                          | V <sub>SYS_MIN</sub> | I <sub>SYS</sub> =0A, V <sub>BAT</sub> <v<sub>SYSMIN=3.5V,</v<sub>                                                                                       | 3.55 | 3.65       | 3.75        | V      |

# AN\_SY6974

|                                                                             |                           | BATFET off, V <sub>SYS</sub> =V <sub>BAT</sub> +150mV              |           |            |            |          |

|-----------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------|-----------|------------|------------|----------|

| Internal High-side Reverse Blocking<br>MOSFET on Resistance                 | R <sub>ON(RBFET)</sub>    |                                                                    |           | 45         |            | mΩ       |

| Internal High-side Switching<br>MOSFET on Resistance between<br>PMID and LX | Ron(HSFET)                |                                                                    |           | 60         |            | mΩ       |

| Internal low-side Switching<br>MOSFET on Resistance between<br>LX and PGND  | R <sub>ON(LSFET)</sub>    |                                                                    |           | 60         |            | mΩ       |

| BATFET Forward Voltage in<br>Supplement Mode                                | V <sub>FWD</sub>          | BAT discharge current 10mA                                         |           | 30         |            | mV       |

| Battery Charger                                                             |                           |                                                                    |           |            |            |          |

| Charge Voltage Regulation<br>Accuracy                                       | VBAT_REG_ACC              | $V_{BAT\_REG} = 4.208V$ and $4.352V$                               | -0.5%     |            | 0.5%       |          |

| Fast Charge Current Regulation<br>Accuracy                                  | I <sub>ICHG_REG_ACC</sub> | V <sub>BAT</sub> =3.8V, I <sub>CHG</sub> =0.72A or 1.38A           | -5.5%     |            | 5.5%       |          |

| Battery LOWV Falling Threshold                                              | VBATLOWV                  | Fast charge to precharge, VBAT falling                             | 2.6       | 2.8        | 2.9        | v        |

| Battery LOWV Rising Threshold                                               | V <sub>BATLOWV_HYST</sub> | Precharge to fast charge, VBAT rising                              | 2.8       | 3.0        | 3.1        | V        |

| Precharge Current Regulation<br>Accuracy                                    | I <sub>PRECHG_ACC</sub>   | $V_{BAT} = 2.6V, I_{CHG} = 180mA$                                  | -15%      |            | 20%        |          |

| Termination Current Accuracy                                                | I <sub>TERM ACC</sub>     | I <sub>TERM</sub> =180mA, I <sub>CHG_REG</sub> >780mA              | -20%      |            | 20%        |          |

|                                                                             | TERM_ACC                  | I <sub>TERM</sub> =60mA, I <sub>CHG_REG</sub> ≤780mA               | -35%      |            | 35%        |          |

| Battery Short Voltage                                                       | VSHORT                    | V <sub>BAT</sub> falling                                           | 1.9       | 2.0        | 2.1        | V        |

| Battery Short Voltage Hysteresis                                            | VSHORT_HYST               | V <sub>BAT</sub> rising                                            |           | 200        |            | mV       |

| Battery Short Current                                                       | Ishort                    | V <sub>BAT</sub> <2.2V                                             | 55        | 100        | 125        | mA       |

| Recharge Threshold Below $V_{BAT\_REG}$                                     | VRECHG                    | $V_{BAT}$ falling, REG04[0] = 0<br>$V_{BAT}$ falling, REG04[0] = 1 | 75<br>160 | 100<br>200 | 145<br>250 | mV<br>mV |

| SYS-BAT MOSFET on Resistance                                                | R <sub>ON_BATFET</sub>    |                                                                    |           | 17         |            | mΩ       |

| Input Voltage/Current Regulation                                            |                           |                                                                    |           |            |            |          |

| Absolute Input Voltage Regulation<br>Accuracy                               | VINDPM_REG_ACC            | set absolute VINDPM=4.5V                                           | -1.5%     |            | 1.5%       |          |

| Input Current Limit Range                                                   | IINDPM_RANGE              |                                                                    | 100       |            | 3200       | mA       |

| USB Input Current Regulation                                                |                           | USB 100mA                                                          | 80        |            | 100        |          |

| Limit, BUS=5V, Current Drawn                                                | IUSB_DPM                  | USB 500mA                                                          | 440       |            | 500        | mA       |

| from LX                                                                     | ,                         | USB 900mA                                                          | 750       |            | 900        |          |

| Input Current Regulation Accuracy                                           | IADPT_DPM                 | I <sup>2</sup> C Set input current limit above 900mA               | -15%      | -7%        | 0%         |          |

| <b>BAT over-Voltage Protection</b>                                          | r                         |                                                                    |           | 1          |            |          |

| Battery over-Voltage Threshold                                              | VBATOVP                   | $V_{BAT}$ rising, as percentage of $V_{BAT\_REG}$                  | 103%      | 104%       | 105%       |          |

| Battery over-Voltage Hysteresis                                             | VBATOVP_HYST              | $V_{BAT}$ falling, as percentage of $V_{BAT\_REG}$                 |           | 2%         |            |          |

| BAT Discharge over-Current Prote                                            | ection                    |                                                                    |           |            |            |          |

| BATFET Discharge over-Current<br>Threshold                                  | IBATFET_OCP               |                                                                    | 7.5       | 10         | 12.5       | А        |

| Thermal Regulation and Thermal S                                            | hutdown                   |                                                                    | T         |            | n          | -        |

| Junction Temperature Regulation<br>Accuracy                                 | TJunction_REG             | REG05[1]=1                                                         |           | 110        |            | C        |

| Thermal Shutdown Rising<br>Temperature                                      | T <sub>TSD</sub>          | Temperature increasing                                             |           | 160        |            | С        |

# AN\_SY6974

|                                                                               | The second secon |                                                                                |       | 20    |           | ~      |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|-------|-----------|--------|

| Thermal Shutdown Hysteresis                                                   | TTSD_HYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                |       | 30    |           | С      |

| JEITA Thermister Comparator                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>Y</b> 7 · · · · · · · · · · · · · · · · · · ·                               |       |       |           |        |

| T1(0 °C) Threshold, Charge<br>Suspended Below this Temp                       | V <sub>T1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>NTC</sub> rising, as percentage to<br>V <sub>REGN</sub> , JEITA_ISET=0  | 72.75 | 73.25 | 73.75     | %      |

| Charge back to $I_{CHG}/2$ and $V_{REG}$ above this Temp                      | V <sub>T1_HYS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Hysteresis, V <sub>NTC</sub> falling,<br>JEITA_ISET=0                          |       | 1.25  |           | %      |

| T2(10 °C) Threshold, Charge back to $I_{CHG}/2$ and $V_{REG}$ below this Temp | V <sub>T2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>NTC</sub> rising, as percentage to<br>V <sub>REGN</sub> , JEITA_ISET=0  | 67.75 | 68.25 | 68.75     | %      |

| Charge back to I <sub>CHG</sub> and V <sub>REG</sub> above this Temp          | VT2_HYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Hysteresis, V <sub>NTC</sub> falling,<br>JEITA_ISET=0                          |       | 1.25  |           | %      |

| T3(45 °C) Threshold, Charge back to $I_{CHG}$ and 4.05V above this Temp       | V <sub>T3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>NTC</sub> falling, as percentage to<br>V <sub>REGN</sub> , JEITA_VSET=0 | 44.25 | 44.75 | 45.25     | %      |

| Charge back to $I_{CHG}$ and $V_{REG}$ below this Temp                        | VT3_HYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Hysteresis, V <sub>NTC</sub> rising,<br>JEITA_VSET=0                           |       | 1.2   |           | %      |

| T4(60 $^{\circ}$ C) Threshold, Charge Suspended above this Temp               | V <sub>T4</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>NTC</sub> falling, as percentage to<br>V <sub>REGN</sub> , JEITA_VSET=0 | 33.7  | 34.2  | 34.7      | %      |

| Charge back to I <sub>CHG</sub> and 4.05V below this Temp                     | V <sub>T4_HYS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Hysteresis, V <sub>NTC</sub> rising,<br>JEITA_VSET=0                           | _     | 1.2   |           | %      |

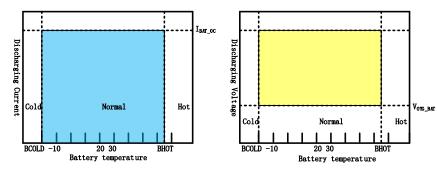

| Boost Mode Thermister Comparato                                               | r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                | -     |       | •         |        |

| Cold Temperature (-20 °C)<br>Threshold 1, NTC pin Voltage<br>Rising Threshold | V <sub>BCOLD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | As Percentage to V <sub>REGN</sub>                                             | 79.5  | 80    | 80.5      | %      |

| Falling Hysteresis                                                            | V <sub>BCOLD_HYS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                |       | 1.25  |           | %      |

| Hot Temperature (65 °C) Threshold<br>2, NTC pin Voltage Falling<br>Threshold  | VBHOT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | As Percentage to V <sub>REGN</sub>                                             | 30.6  | 31.1  | 31.6      | %      |

| Rising Hysteresis                                                             | V <sub>BHOT_HYS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                |       | 3     |           | %      |

| Buck Mode Operations                                                          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                |       |       |           |        |

| HSFET Cycle-by-cycle Current<br>Limit                                         | IHSFET_OCP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                |       | 6     |           | А      |

| PWM Switching Frequency                                                       | F <sub>SW</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                | 1300  | 1500  | 1700      | kHz    |

| Boost Mode Operations                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |       |       |           |        |

| PWM Switching Frequency                                                       | F <sub>SW_BOOST</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $V_{BAT}=3.2V, V_{BUS}=5V, I_{BUS}=1A$                                         | 1300  | 1500  | 1700      | kHz    |

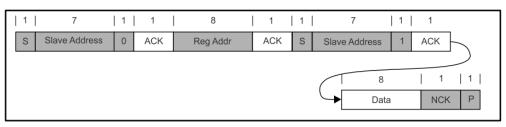

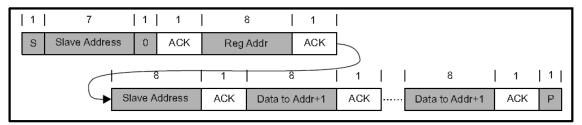

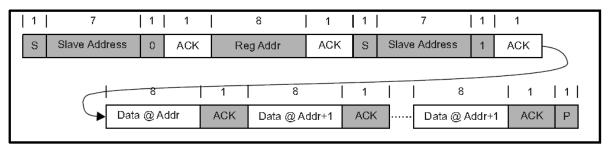

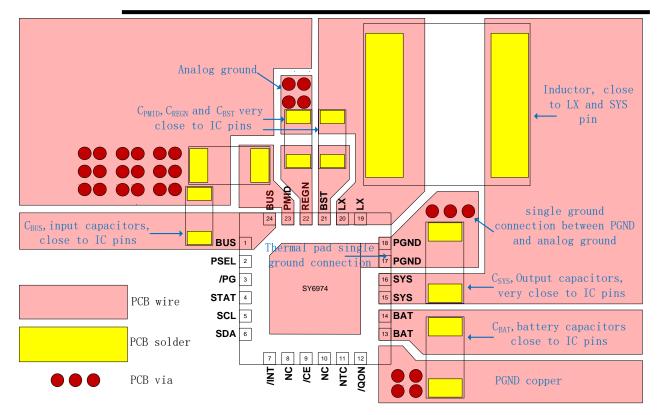

| OTG Output Voltage Range                                                      | Votg_reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I <sub>BUS</sub> =0A                                                           | 4.85  |       | 5.3       | V      |