ADVANCE DATASHEET

SGM90516 High-Density, 12-Bit Analog Monitor and Control Solution with Multichannel ADC, Bipolar DACs, Temperature Sensor, and GPIO Ports

## **GENERAL DESCRIPTION**

The SGM90516 is a high integrated analog front end, which includes 12-bit 16 channels digital-to-analog converters (DACs), a 12-bit 21 channels inputs successive approximation (SAR) analog-to-digital converter (ADC), a temperature sensor and an on-chip reference.

The chip also has 8 channels general purpose inputs and outputs (GPIOs). These pins are configurable for ADC inputs or GPIOs.

The chip is operated by a 4-wire SPI-compatible interface.

The SGM90516 is available in a Green TQFP-10×10-64L (Exposed Pad) package. It is specified from -40°C to +125°C.

## **APPLICATIONS**

Active Antenna System mMIMO Distributed Antenna Systems Macro Remote Radio Unit Radar Outdoor Backhaul Unit

Data Acquisition Systems

## FEATURES

- 16 Monotonic 12-Bit DACs

- Programmable Voltage Ranges: -10V to 0V,

-5V to 0V, 0V to 5V, and 0V to 10V

- + High Current Drive Capability: up to ±15mA

- Auto-Range Detector

- Selectable Clamp Voltage

- 12-Bit SAR ADC

- 21 External Analog Inputs

16 Bipolar Inputs: -12.5V to +12.5V

5 High-Precision Inputs: 0V to 5V

- Programmable Out-of-Range Alarms

- Internal 2.5V Reference

- Internal Temperature Sensor

- -40°C to +125°C Operation

- ±3°C Accuracy

- Eight General-Purpose I/O Ports (GPIOs)

- Low-Power SPI-Compatible Serial Interface

- 4-Wire Mode, 1.8V to 5.25V Operation

- -40°C to +125°C Operating Temperature Range

- Available in a Green TQFP-10×10-64L (Exposed Pad) Package

### **PACKAGE/ORDERING INFORMATION**

| MODEL    | PACKAGE<br>DESCRIPTION          | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING     | PACKING<br>OPTION   |  |

|----------|---------------------------------|-----------------------------------|--------------------|------------------------|---------------------|--|

| SGM90516 | TQFP-10×10-64L<br>(Exposed Pad) | -40°C to +125°C                   | SGM90516XTFF64G/TR | 05Q<br>XTFF64<br>XXXXX | Tape and Reel, 1000 |  |

### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

XXXXX

Vendor Code

- Trace Code

- Date Code Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

-0.31/ to 61/

### **ABSOLUTE MAXIMUM RATINGS**

Voltage Range

| AVDD to GND                               | 0.3V to 6V                  |

|-------------------------------------------|-----------------------------|

| DVDD to GND                               | 0.3V to 6V                  |

| IOVDD to GND                              | 0.3V to 6V                  |

| AVCC to GND                               | 0.3V to 18V                 |

| AVEE to GND                               | 13V to 0.3V                 |

| AVSSB, AVSSC, AVSSD to AVEE               | 0.3V to 13V                 |

| AVCC to AVSSB, AVSSC, or AVSSD            | 0.3V to 26V                 |

| AVCC to AVEE                              | 0.3V to 26V                 |

| DGND to AGND                              | 0.3V to 0.3V                |

| ADC_[0-15] Analog Input Voltage to GND    | 13V to 13V                  |

| LV_ADC[16-20] Analog Input Voltage to GND | )                           |

| -0.3V                                     | to V <sub>AVDD</sub> + 0.3V |

| DAC_A[0-3] Outputs to GND                 |                             |

| V <sub>AVEE</sub> - 0.3V                  | to V <sub>AVCC</sub> + 0.3V |

| DAC_B[4-7] Outputs to GND                 |                             |

|                                           | to V <sub>AVCC</sub> + 0.3V |

| DAC_C[8-11] Outputs to GND                |                             |

|                                           | to V <sub>AVCC</sub> + 0.3V |

| DAC_D[12-15] Outputs to GND               |                             |

| V <sub>AVSSD</sub> - 0.3V                 |                             |

| REF_CMP to GND0.3V                        | to V <sub>AVDD</sub> + 0.3V |

| CS, SCLK, SDI and RESET to GND            |                             |

| -0.3V t                                   |                             |

| SDO to GND0.3V t                          |                             |

| GPIO[0-7] to GND0.3V t                    |                             |

| ADC_[0:15] Analog Input Current           |                             |

| LV_ADC[16:20] Analog Input Current        |                             |

| GPIO[0:7] Sinking Current                 |                             |

| Junction Temperature                      |                             |

| Storage Temperature Range6                |                             |

| Lead Temperature (Soldering, 10s)         | +260°C                      |

|                                           |                             |

## RECOMMENDED OPERATING CONDITIONS

| V <sub>AVDD</sub>                                            |                         |

|--------------------------------------------------------------|-------------------------|

| V <sub>DVDD</sub> <sup>(1)</sup>                             | 4.7V to 5.5V            |

| V <sub>IOVDD</sub> <sup>(2)</sup>                            | 1.8V to 5.5V            |

| V <sub>AVCC</sub>                                            | 4.7V to 12.5V           |

| V <sub>AVEE</sub>                                            | 12.5V to 0V             |

| V <sub>AVSSB</sub> , V <sub>AVSSC</sub> , V <sub>AVSSD</sub> | V <sub>AVEE</sub> to 0V |

| Specified Operating Temperature Range.                       | 40°C to +105°C          |

| Operating Temperature Range                                  | 40°C to +125°C          |

|                                                              |                         |

### NOTES:

1. The value of the DVDD pin must be equal to that of the AVDD pin.

2. The value of the IOVDD pin must be less than or equal to that of the DVDD pin.

### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

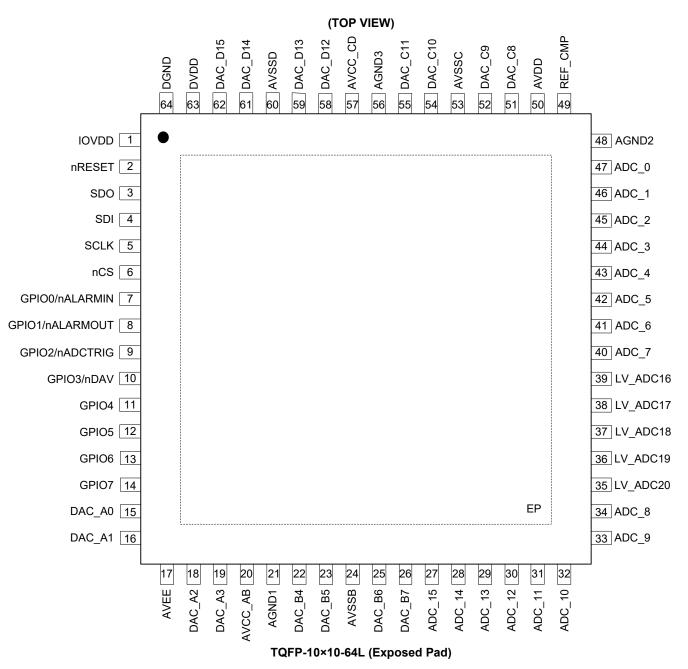

### **PIN CONFIGURATION**

### **PIN DESCRIPTION**

| PIN | NAME            | I/O | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-----|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | IOVDD           | I   | Digital Interface Input/Output Power Supply. It can be operated from 1.8V to 5.25V.<br>The voltage on this pin must not be greater than the value of the DVDD pin.                                                                                                                                                                                                                                                                                                                              |  |  |

| 2   | nRESET          | Ι   | It's a hardware reset input pin. It's active low.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 3   | SDO             | 0   | Serial Data Output pin. When CS pin is pulled high, SDO is in high impedance. When CS pin is low, the data is shifted out by this pin at each falling edge of the SCLK.                                                                                                                                                                                                                                                                                                                         |  |  |

| 4   | SDI             | I   | Serial Data Input pin. Data is shifted in at each rising edged of the SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 5   | SCLK            | I   | Serial Interface Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 6   | nCS             | Ι   | It's chip select pin. This pin also works as the data frame synchronization signal.<br>When it's pulled low, it enables the serial interface operation.                                                                                                                                                                                                                                                                                                                                         |  |  |

| 7   | GPIO0/nALARMIN  | I/O | General Purpose Digital Input/Output Pin0 (default). It's a bidirectional pin which has an internal $48k\Omega$ resistor pulled up to IOVDD. This pin can be alternatively configured as nALARMIN input pin, which is an active low input signal. If it's not used, this pin can be floated.                                                                                                                                                                                                    |  |  |

| 8   | GPIO1/nALARMOUT | I/O | General Purpose Digital Input/Output Pin1 (default). It's a bidirectional pin which has an internal $48k\Omega$ resistor pulled up to IOVDD. This pin can be alternatively configured as nALARMOUT output pin, which is an open drain output. If there is an alarm event is generated, it outputs active low. If it's not used, this pin can be floated.                                                                                                                                        |  |  |

| 9   | GPIO2/nADCTRIG  | I/O | General Purpose Digital Input/Output Pin2 (default). It's a bidirectional pin wh has an internal $48k\Omega$ resistor pulled up to IOVDD. This pin can be alternativ configured as nADCTRIG input pin, which is an active low input signal. The fall edge of this pin begins the sampling and conversion of the ADC. If it's not used, t pin can be floated.                                                                                                                                    |  |  |

| 10  | GPIO3/nDAV      | I/O | General Purpose Digital Input/Output Pin3 (default). It's a bidirectional pin<br>has an internal $48k\Omega$ resistor pulled up to IOVDD. This pin can be altern<br>configured as nDAV output pin, which is an active low signal indicate<br>available. When in direct mode, the nDAV goes low if the conversion ends. W<br>auto mode, a 1us pulse will appear on this pin if a conversion cycle finished<br>it is in deactivated, nDAV pin remains high. If it's not used, this pin can be flo |  |  |

| 11  | GPIO4           | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 12  | GPIO5           | I/O | General Purpose Digital Input/Output. These pins are bidirectional pins which have an internal $48k\Omega$ resistor pulled up to IOVDD. If they are not used, these pins can                                                                                                                                                                                                                                                                                                                    |  |  |

| 13  | GPIO6           | I/O | be floated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 14  | GPIO7           | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 15  | DAC_A0          | 0   | DAC Group A. These DAC channels share the same range and clamp voltage. If                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 16  | DAC_A1          | 0   | any of the other DAC groups is in a negative voltage range, DAC group A should be in a negative voltage range as well.                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 17  | AVEE            | I   | Lowest Potential in the System. This pin is typically tied to a negative suppl voltage but if all DACs are set in a positive output range, this pin can be connecte to the analog ground. This pin also acts as the negative power supply for DAC group A. This pin sets the power-on-reset and clamp voltage values for the DAC group A.                                                                                                                                                       |  |  |

| 18  | DAC_A2          | 0   | DAC Group A. These DAC channels share the same range and clamp voltage. If                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 19  | DAC_A3          | 0   | any of the other DAC groups is in a negative voltage range, DAC group A should be in a negative voltage range as well.                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 20  | AVCC_AB         | Ι   | Positive Analog Power for DAC Groups A and B. The AVCC_AB and AVCC_CD pins must be connected to the same potential (AVCC).                                                                                                                                                                                                                                                                                                                                                                      |  |  |

## **PIN DESCRIPTION (continued)**

| PIN | NAME                                                                    | I/O | FUNCTION                                                                                                                                                                                                                                                                                        |

|-----|-------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21  | AGND1                                                                   | I   | Analog Ground. The pin is the ground reference point for all analog circuitry on the device. Connect the AGND1, AGND2, and AGND3 pins to the same potential (AGND). Ideally, the analog and digital grounds should be at the same potential (GND) and must not differ by more than $\pm 0.3V$ . |

| 22  | DAC_B4                                                                  | 0   | DAC Group B. These DAC channels share the same range and clamp voltage.                                                                                                                                                                                                                         |

| 23  | DAC_B5                                                                  | 0   | DAG Gloup B. These DAG channels share the same range and clamp voltage.                                                                                                                                                                                                                         |

| 24  | AVSSB                                                                   | I   | Negative Analog Supply for DAC Group B. This pin sets the power-on-reset and clamp voltage values for the DAC group B. This pin is typically tied to the AVEE pin for the negative output ranges or AGND for the positive output ranges.                                                        |

| 25  | DAC_B6                                                                  | 0   | DAC Crown R. Those DAC channels share the same range and slamp voltage                                                                                                                                                                                                                          |

| 26  | DAC_B7                                                                  | 0   | DAC Group B. These DAC channels share the same range and clamp voltage.                                                                                                                                                                                                                         |

| 27  | ADC_15                                                                  | I   |                                                                                                                                                                                                                                                                                                 |

| 28  | ADC_14                                                                  | I   | Bipolar Analog Inputs. These pins are typically used to monitor the DAC group-A                                                                                                                                                                                                                 |

| 29  | 29 ADC_13                                                               |     | outputs. The input range of these channels is -12.5V to 12.5V.                                                                                                                                                                                                                                  |

| 30  | ADC_12                                                                  | I   |                                                                                                                                                                                                                                                                                                 |

| 31  | ADC_11                                                                  | I   |                                                                                                                                                                                                                                                                                                 |

| 32  | ADC_10                                                                  | I   | Bipolar Analog Inputs. These pins are typically used to monitor the DAC group B                                                                                                                                                                                                                 |

| 33  | 33 ADC_9                                                                |     | outputs. The input range of these channels is -12.5V to 12.5V.                                                                                                                                                                                                                                  |

| 34  | ADC_8                                                                   | I   |                                                                                                                                                                                                                                                                                                 |

| 35  | LV_ADC20                                                                | I   |                                                                                                                                                                                                                                                                                                 |

| 36  | LV_ADC19                                                                | I   |                                                                                                                                                                                                                                                                                                 |

| 37  | LV_ADC18                                                                | I   | General Purpose Analog Inputs. These channels are used for general monitoring. The input range of these pins is 0 to $2 \times V_{REF}$ .                                                                                                                                                       |

| 38  | LV_ADC17                                                                | I   |                                                                                                                                                                                                                                                                                                 |

| 39  | LV_ADC16                                                                | I   |                                                                                                                                                                                                                                                                                                 |

| 40  | ADC_7                                                                   | I   |                                                                                                                                                                                                                                                                                                 |

| 41  | ADC_6                                                                   | I   | Bipolar Analog Inputs. These pins are typically used to monitor the DAC group D                                                                                                                                                                                                                 |

| 42  | ADC_5                                                                   | I   | outputs. The input range of these channels is -12.5V to 12.5V.                                                                                                                                                                                                                                  |

| 43  | ADC_4                                                                   | I   |                                                                                                                                                                                                                                                                                                 |

| 44  | ADC_3                                                                   | I   |                                                                                                                                                                                                                                                                                                 |

| 45  | ADC_2 I Bipolar Analog Inputs. These pips are typically used to monitor |     | Bipolar Analog Inputs. These pins are typically used to monitor the DAC group C                                                                                                                                                                                                                 |

| 46  | ADC_1                                                                   | I   | outputs. The input range of these channels is -12.5V to 12.5V.                                                                                                                                                                                                                                  |

| 47  | ADC_0                                                                   | I   |                                                                                                                                                                                                                                                                                                 |

## **PIN DESCRIPTION (continued)**

| PIN            | NAME    | I/O | FUNCTION                                                                                                                                                                                                                                                                                        |  |  |  |

|----------------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 48             | AGND2   | I   | Analog Ground. The pin is the ground reference point for all analog circuitry on the device. Connect the AGND1, AGND2, and AGND3 pins to the same potential (AGND). Ideally, the analog and digital grounds should be at the same potential (GND) and must not differ by more than $\pm 0.3V$ . |  |  |  |

| 49             | REF_CMP | 0   | Internal Reference Compensation Capacitor Connection. Connect a 4.7µF capacitor between this pin and the AGND2 pin.                                                                                                                                                                             |  |  |  |

| 50             | AVDD    | Ι   | Analog Supply Voltage (4.7V to 5.5V). This pin must have the same value as the DVDD pin.                                                                                                                                                                                                        |  |  |  |

| 51             | DAC_C8  | 0   | DAC Group C. These DAC channels share the same range and clamp voltage.                                                                                                                                                                                                                         |  |  |  |

| 52             | DAC_C9  | 0   | DAC Group C. These DAC channels share the same range and clamp voltage.                                                                                                                                                                                                                         |  |  |  |

| 53             | AVSSC   | I   | Negative Analog Supply for DAC Group C. This pin sets the power on reset a<br>clamp voltage values for the DAC group C. This pin is typically tied to the AVEE p<br>for the negative output ranges or AGND for the positive output ranges.                                                      |  |  |  |

| 54             | DAC_C10 | 0   |                                                                                                                                                                                                                                                                                                 |  |  |  |

| 55             | DAC_C11 | 0   | DAC Group C. These DAC channels share the same range and clamp voltage.                                                                                                                                                                                                                         |  |  |  |

| 56             | AGND3   | I   | Analog Ground. The pin is the ground reference point for all analog circuitry o device. Connect the AGND1, AGND2, and AGND3 pins to the same pote (AGND). Ideally, the analog and digital grounds should be at the same pote (GND) and must not differ by more than ±0.3V.                      |  |  |  |

| 57             | AVCC_CD | I   | Positive analog power for DAC groups C and D. The AVCC_AB and AVCC_CD pins must be connected to the same potential (AVCC).                                                                                                                                                                      |  |  |  |

| 58             | DAC_D12 | 0   | DAC Group D. These DAC channels share the same range and clamp voltage.                                                                                                                                                                                                                         |  |  |  |

| 59             | DAC_D13 | 0   | DAC Group D. These DAC channels share the same range and clamp voltage.                                                                                                                                                                                                                         |  |  |  |

| 60             | AVSSD   | Ι   | Negative Analog Supply for DAC Group D. This pin sets the power on reset and clamp voltage values for the DAC group D. This pin is typically tied to the AVEE pin for the negative output ranges or AGND for the positive output ranges.                                                        |  |  |  |

| 61             | DAC_D14 | 0   | DAC Group D. These DAC channels share the same range and clamp voltage.                                                                                                                                                                                                                         |  |  |  |

| 62             | DAC_D15 | 0   | DAC Group D. These DAC channels share the same range and clamp voltage.                                                                                                                                                                                                                         |  |  |  |

| 63             | DVDD    | I   | Digital Supply Voltage (4.7V to 5.5V). This pin must have the same value as the AVDD pin.                                                                                                                                                                                                       |  |  |  |

| 64             | DGND    | I   | Digital Ground. This pin is the ground reference point for all digital circuitry on the device. Ideally, the analog and digital grounds should be at the same potential (GND) and must not differ by more than $\pm 0.3V$ .                                                                     |  |  |  |

| Thermal<br>Pad | EP      | I   | The thermal pad is located on the bottom side of the device package. The thermal pad should be tied to the same potential as the AVEF pin or left disconnected.                                                                                                                                 |  |  |  |

## ELECTRICAL CHARACTERISTICS

(The electrical ratings specified in this section apply to all specifications in this document, unless otherwise noted. These specifications are interpreted as conditions that do not degrade the device parametric or functional specifications for the life of the product containing it.  $V_{AVDD} = V_{DVDD} = 4.7V$  to 5.5V,  $V_{AVCC} = 12V$ ,  $V_{IOVDD} = 1.8V$  to 5.25V, AGND = DGND = 0V,  $V_{AVEE} = V_{AVSSB} = V_{AVSSC} = V_{AVSSD} = -12V$  (for DAC groups in negative range) or 0 V (for DAC groups in positive ranges), DAC output range = 0V to 10V for all groups no load on the DACs. To = -40°C, to +105°C)

| PARAMETER                                   |                        | CONDITIONS                                                                              | MIN | ТҮР   | MAX | UNITS  |  |

|---------------------------------------------|------------------------|-----------------------------------------------------------------------------------------|-----|-------|-----|--------|--|

| DAC DC Accuracy                             | •                      | ·                                                                                       |     | •     |     |        |  |

| Resolution                                  |                        |                                                                                         | 12  |       |     | Bits   |  |

| Relative Accuracy (INL)                     | 10V and -10            | / line passing through codes 020h and FFFh. 0V to<br>V to 0V ranges                     |     | ±0.3  |     | LSB    |  |

| Relative Accuracy (INE)                     | 5V and -5V t           | / line passing through codes 040h and FFFh. 0V to o 0V ranges                           |     | ±0.5  |     | LSD    |  |

| Differential Nonlinearity (DNL)             | 020h and FF            | photonic. Measured by line passing through codes<br>Fh. 0V to 10V and -10V to 0V ranges |     | ±0.03 |     | LSB    |  |

|                                             |                        | onotonic. Measured by line passing through codes<br>Fh. 0V to 5V and -5V to 0V ranges   |     | ±0.06 |     | LOD    |  |

|                                             |                        | 0V to 10V range                                                                         |     | ±2.5  |     |        |  |

| Total Unadjusted Error <sup>(1)</sup> (TUE) | T <sub>A</sub> = +25°C | -10V to 0V range                                                                        |     | ±2.5  |     | - mV   |  |

|                                             | 1 <sub>A</sub> = +23 C | 0V to 5V range                                                                          |     | ±1.5  |     |        |  |

|                                             |                        | -5V to 0V range                                                                         |     | ±1.5  |     |        |  |

| Offset Error                                |                        | Measured by line passing through codes 020h and FFFh. 0V to 10V range                   |     | ±0.25 |     | m)/    |  |

|                                             |                        | Measured by line passing through codes 040h and FFFh. 0V to 5V range                    |     | ±0.25 |     | - mV   |  |

| Zero-Code Error                             | T <sub>A</sub> = +25°C | Code 000h, -10V to 0V range                                                             |     | ±1    |     | mV     |  |

|                                             |                        | Code 000h, -5V to 0V range                                                              |     | ±1    |     |        |  |

|                                             |                        | Measured by line passing through codes 020h and FFFh, 0V to 10V range                   |     | ±0.01 |     |        |  |

| Gain Error <sup>(1)</sup>                   |                        | Measured by line passing through codes 020h and FFFh, -10V to 0V range                  |     | ±0.01 |     | - %FSR |  |

|                                             |                        | Measured by line passing through codes 040h and FFFh, 0V to 5V range                    |     | ±0.01 |     |        |  |

|                                             |                        | Measured by line passing through codes 040h and FFFh, -5V to 0V range                   |     | ±0.01 |     |        |  |

| Offset Temperature Coefficient              | 0V to 10V range        |                                                                                         |     | ±1    |     | nnm/°C |  |

|                                             | 0V to 5V range         |                                                                                         |     | ±1    |     | ppm/°C |  |

| Zero-Code Temperature Coefficient           | -10V to 0V range       |                                                                                         |     | ±2    |     |        |  |

| Zero-Code Temperature Coemcient             | -5V to 0V range        |                                                                                         |     | ±2    |     | ppm/°C |  |

|                                             | 0V to 10V range        |                                                                                         |     | ±2.5  |     |        |  |

| Gain Temperature Coefficient <sup>(1)</sup> | -10V to 0V ra          | ange                                                                                    |     | ±2.5  |     | ppm/°C |  |

|                                             | 0V to 5V ran           | ge                                                                                      |     | ±2.5  |     |        |  |

|                                             | -5V to 0V rai          | nge                                                                                     |     | ±2.5  |     |        |  |

### NOTE:

1. The internal reference contribution not included.

## **ELECTRICAL CHARACTERISTICS (continued)**

### DAC (continued)

(The electrical ratings specified in this section apply to all specifications in this document, unless otherwise noted. These specifications are interpreted as conditions that do not degrade the device parametric or functional specifications for the life of the product containing it.  $V_{AVDD} = V_{DVDD} = 4.7V$  to 5.5V,  $V_{AVCC} = 12V$ ,  $V_{IOVDD} = 1.8V$  to 5.25V, AGND = DGND = 0V,  $V_{AVEE} = V_{AVSSB} = V_{AVSSC} = V_{AVSSD} = -12V$  (for DAC groups in negative range) or 0 V (for DAC groups in positive ranges), DAC output range = 0V to 10V for all groups, no load on the DACs,  $T_A = -40^{\circ}$ C to +105°C)

| PARAMETER                                      | CONDITIONS                                                                                                                                                                                            | MIN              | TYP                   | MAX | UNITS            |  |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-----|------------------|--|

| DAC Output Characteristics                     |                                                                                                                                                                                                       |                  |                       |     |                  |  |

| Full-Scale Output Voltage Range <sup>(2)</sup> | Set at power-up or reset through auto-range detection. The output range can be modified after power-up or reset through the DAC range registers (Address 0x1E through 0x1F). DAC-RANGE = 100b         |                  |                       | 0   |                  |  |

|                                                | The output range can be modified after power-up or rese<br>through the DAC range registers (Address 0x1E through 0x1F)<br>DAC-RANGE = 101b                                                            |                  | 0                     |     |                  |  |

|                                                | Set at power-up or reset through auto-range detection. The<br>output range can be modified after power-up or reset through the<br>DAC range registers (Address 0x1E through 0x1F)<br>DAC-RANGE = 111b | e 0              |                       | 5   | - V              |  |

|                                                | The output range can be modified after power-up or rese<br>through the DAC range registers (Address 0x1E through 0x1F)<br>DAC-RANGE = 110b                                                            |                  |                       | 10  |                  |  |

|                                                | Transition: Code 400h to C00h to within $\frac{1}{2}$ LSB, R <sub>L</sub> = 2k $\Omega$ , C <sub>L</sub> = 200pF. 0V to 10V and -10V to 0 V ranges                                                    |                  | 10                    |     |                  |  |

| Output Voltage Settling Time                   | Transition: Code 400h to C00h to within ½ LSB, $R_L = 2k\Omega$ , $C_L = 200pF$ . 0V to 5V and -5V to 0V ranges                                                                                       |                  | 10                    |     | μs               |  |

| Slew Rate                                      | Transition: Code 400h to C00h, 10% to 90%, $R_L = 2k\Omega$ , $C_L = 200pF$ . 0V to 10V and -10V to 0V ranges                                                                                         |                  | 1.25                  |     | — V/μs           |  |

|                                                | Transition: Code 400h to C00h, 10% to 90%, R<br>C <sub>L</sub> = 200pF. 0V to 5V and -5V to 0V ranges                                                                                                 |                  | 1.25                  |     |                  |  |

| Short Circuit Current                          | Full-scale current shorted to the DAC group AVSS or AVCC voltage                                                                                                                                      |                  | ±45                   |     | mA               |  |

| Load Current <sup>(3)</sup>                    | Source or sink with 1V headroom from the DAC group AVCC o<br>AVSS voltage, voltage drop < 25mV                                                                                                        | ±15              |                       |     | mA               |  |

| Load Guilent                                   | Source or sink with 300mV headroom from the DAC group<br>AVCC or AVSS voltage, voltage drop < 25mV                                                                                                    | <sup>0</sup> ±10 |                       |     |                  |  |

| Maximum Capacitive Load (4)                    | $R_L = \infty$ , the capability of load of cap directly.                                                                                                                                              | 0                |                       | 10  | nF               |  |

| DC Output Impedance                            | Code set to 800h, ±15mA                                                                                                                                                                               |                  | 1                     |     | Ω                |  |

| Power-On Overshoot                             | $V_{AVEE} = V_{AVSSB} = V_{AVSSC} = V_{AVSSD} = AGND, V_{AVCC} = 0V to 12V, 2ms ramp$                                                                                                                 | 6                | 10                    |     | mV               |  |

| Glitch Energy                                  | Transition: Code 7FFh to 800h; 800h to 7FFh                                                                                                                                                           |                  | 1                     |     | nV-s             |  |

|                                                | 1kHz, code 800h, includes internal reference noise                                                                                                                                                    |                  | 520                   |     | $nV/\sqrt{Hz}$   |  |

| Output Noise                                   | $T_A = +25^{\circ}C$ integrated noise from 0.1Hz to 10Hz, code 800h includes internal reference noise                                                                                                 | ,                | 20                    |     | μV <sub>PP</sub> |  |

| Clamp Outputs                                  |                                                                                                                                                                                                       |                  |                       |     |                  |  |

|                                                | DAC output range: 0V to 10V, V <sub>AVSS</sub> = AGND                                                                                                                                                 |                  | 0                     |     |                  |  |

| Clamp Output Voltage (5)                       | DAC output range: 0V to 5V, V <sub>AVSS</sub> = AGND                                                                                                                                                  |                  | 0                     |     | V                |  |

|                                                | DAC output range: -10V to 0V, V <sub>AVSS</sub> = -12V                                                                                                                                                |                  | V <sub>AVSS</sub> + 2 |     |                  |  |

|                                                | DAC output range: -5V to 0V, $V_{AVSS}$ = -6V                                                                                                                                                         |                  | V <sub>AVSS</sub> + 1 |     |                  |  |

| Clamp Output Impedance                         |                                                                                                                                                                                                       |                  | 200                   |     | Ω                |  |

### NOTES:

2. The output voltage of each DAC group must not be greater than that of the corresponding AVCC pin (AVCC\_AB or AVCC\_CD) or lower than that of the corresponding AVSS pin (AVEE, AVSSB, AVSSC or AVSSD). See the DAC Output Range and Clamp Configuration section for more details.

3. If all channels are simultaneously loaded, care must be taken to ensure the thermal conditions for the device are not exceeded.

4. To be sampled during initial release to ensure compliance; not subject to production testing.

5. No DAC load to the DAC group AVSS pin.

## **ELECTRICAL CHARACTERISTICS (continued)**

### ADC and Temperature Sensor

(The electrical ratings specified in this section apply to all specifications in this document, unless otherwise noted. These specifications are interpreted as conditions that do not degrade the device parametric or functional specifications for the life of the product containing it.  $V_{AVDD} = V_{DVDD} = 4.7V$  to 5.5V,  $V_{AVCC} = 12V$ ,  $V_{IOVDD} = 1.8V$  to 5.25V, AGND = DGND = 0V,  $V_{AVEE} = V_{AVSSB} = V_{AVSSC} = V_{AVSSD} = -12V$  (for DAC groups in negative range) or 0 V (for DAC groups in positive ranges), DAC output range = 0V to 10V for all groups, no load on the DACs,  $T_A = -40^{\circ}$ C to +105°C)

| PARAMETER                           | CONDITIONS                                              | MIN        | TYP   | MAX                     | UNITS  |

|-------------------------------------|---------------------------------------------------------|------------|-------|-------------------------|--------|

| Resolution                          |                                                         | 12         |       |                         | Bits   |

| late and Merclin equity             | Unipolar input channels                                 |            | ±0.5  |                         |        |

| Integral Nonlinearity               | Bipolar input channels                                  |            | ±0.5  |                         | LSB    |

| Differential Nonlinearity           | Specified monotonic. All input channels                 |            | ±0.5  |                         | LSB    |

| Unipolar Analog Inputs: LV_ADC1     | 6 to LV_ADC20                                           |            |       |                         |        |

| Absolute Input Voltage Range        |                                                         | AGND - 0.2 |       | V <sub>AVDD</sub> + 0.2 | V      |

| Full Scale Input Range              | V <sub>REF</sub> measured at REF_CMP pin                | 0          |       | $2 \times V_{REF}$      | V      |

| Input Capacitance                   |                                                         |            | 34    |                         | pF     |

| DC Input Leakage Current            | Unselected ADC input                                    |            |       | ±10                     | μA     |

| Offset Error                        |                                                         |            | ±1    |                         | LSB    |

| Offset Error Match                  |                                                         |            | ±0.5  |                         | LSB    |

| Gain Error <sup>(1)</sup>           |                                                         |            | ±0.5  |                         | LSB    |

| Gain Error Match                    |                                                         |            | ±1    |                         | LSB    |

| Update Time                         | Single unipolar input, temperature sensor disabled      |            | 11.5  |                         | μs     |

| Bipolar Analog Inputs: ADC_0 to A   | ADC_15                                                  | 1 1        |       |                         | 1      |

| Absolute Input Voltage Range        |                                                         | -13        |       | 13                      | V      |

| Full Scale Input Range              |                                                         | -12.5      |       | 12.5                    | V      |

| Input Resistance                    |                                                         |            | 175   |                         | kΩ     |

| Offset Error                        |                                                         |            | ±0.25 |                         | LSB    |

| Gain Error <sup>(1)</sup>           |                                                         |            | ±0.5  |                         | LSB    |

| Update Time                         | Single bipolar input, temperature sensor disabled       |            | 25    |                         | μs     |

| Temperature Sensor                  |                                                         | 1 1        |       |                         |        |

| Operating Range                     |                                                         | -40        |       | 125                     | C°     |

| Accuracy                            | T <sub>A</sub> = -40°C to +125°C, AVDD = 5V             |            | ±1.25 |                         | °C     |

| Resolution                          | LSB size                                                |            | 0.25  |                         | °C     |

| Update Time                         | All ADC input channels disabled                         |            | 256   |                         | μs     |

| ADC Update Time                     |                                                         | 11         |       |                         |        |

| Internal Oscillator Frequency       |                                                         |            | 4     |                         | MHz    |

|                                     | All 21 ADC inputs enabled, temperature sensor disabled. |            | 609.5 |                         | μs     |

| ADC Update Time                     | All 21 ADC inputs enabled, temperature sensor enabled.  |            | 865.5 |                         | μs     |

| Internal Reference (Internal Refere | ence Not Accessible)                                    | 1 1        |       |                         | 1      |

| Initial Accuracy                    | T <sub>A</sub> = +25°C                                  |            | 2.5   |                         | V      |

| Reference Temperature Coefficient   |                                                         |            | 12    |                         | ppm/°C |

### NOTE:

1. The internal reference contribution not included.

## **ELECTRICAL CHARACTERISTICS (continued)**

### General

(The electrical ratings specified in this section apply to all specifications in this document, unless otherwise noted. These specifications are interpreted as conditions that do not degrade the device parametric or functional specifications for the life of the product containing it.  $V_{AVDD} = V_{DVDD} = 4.7V$  to 5.5V,  $V_{AVCC} = 12V$ ,  $V_{IOVDD} = 1.8V$  to 5.25V, AGND = DGND = 0V,  $V_{AVEE} = V_{AVSSB} = V_{AVSSC} = V_{AVSSD} = -12V$  (for DAC groups in negative range) or 0 V (for DAC groups in positive ranges), DAC output range = 0V to 10V for all groups no load on the DACs. To = -40°C, to +105°C)

| PARAMETER                                     | CONDITIONS                                                                     | MIN                      | TYP   | MAX                     | UNITS |

|-----------------------------------------------|--------------------------------------------------------------------------------|--------------------------|-------|-------------------------|-------|

| AVSS Detector                                 | •                                                                              |                          |       |                         |       |

| AVSS Threshold Detector (AV <sub>SSTH</sub> ) |                                                                                | -3.5                     |       | -1.5                    | V     |

| Digital Logic: GPIO                           | •                                                                              |                          |       | -                       |       |

| High-Level Input Voltage                      | $V_{IOVDD} = 1.8V$ to 5.5V                                                     | $0.7 \times V_{IOVDD}$   |       |                         | V     |

|                                               | V <sub>IOVDD</sub> = 1.8V                                                      |                          |       | 0.45                    | V     |

| Low-Level Input Voltage                       | $V_{IOVDD} = 2.7V$ to 5.5V                                                     |                          |       | 0.3 ×V <sub>IOVDD</sub> | v     |

| Low-Level Output Voltage                      | $V_{IOVDD}$ = 1.8V, $I_{LOAD}$ = -2mA                                          |                          |       | 0.4                     | V     |

|                                               | $V_{IOVDD}$ = 5.5V, $I_{LOAD}$ = -5mA                                          |                          |       | 0.4                     | V     |

| Input Impedance                               | To IOVDD                                                                       |                          | 48    |                         | kΩ    |

| Digital Logic: All Except GPIO                | •                                                                              |                          |       |                         |       |

| High-Level Input Voltage                      | $V_{IOVDD} = 1.8V$ to 5.5V                                                     | $0.7 \times V_{IOVDD}$   |       |                         | V     |

|                                               | V <sub>IOVDD</sub> = 1.8V                                                      |                          |       | 0.45                    | V     |

| Low-Level Input Voltage                       | $V_{IOVDD} = 2.7V$ to 5.5V                                                     |                          |       | $0.3 \times V_{IOVDD}$  | V     |

| High-Level Output Voltage                     | I <sub>LOAD</sub> = -1mA                                                       | V <sub>IOVDD</sub> - 0.4 |       |                         | V     |

| Low-Level Output Voltage                      | I <sub>LOAD</sub> = 1mA                                                        |                          |       | 0.4                     | V     |

| High Impedance Leakage                        |                                                                                |                          |       | ±5                      | μA    |

| High Impedance Output Capacitance             |                                                                                |                          | 10    |                         | pF    |

| Power Requirements                            | •                                                                              |                          |       |                         |       |

| AVDD Supply Current (I <sub>AVDD</sub> )      |                                                                                |                          | 6     |                         |       |

| AVCC Supply Current (I <sub>AVCC</sub> )      |                                                                                |                          | 7.5   |                         | mA    |

| AVSS Supply Current (I <sub>AVSS</sub> )      |                                                                                |                          | -5    |                         |       |

| AVEE Supply Current (I <sub>AVEE</sub> )      | No DAC load, all DACs at 800h code and ADC at the fastest auto conversion rate |                          | -1.75 |                         |       |

| DVDD Supply Current (I <sub>DVDD</sub> )      |                                                                                |                          | 1     |                         |       |

| IOVDD Supply Current (I <sub>IODD</sub> )     |                                                                                |                          | 1.5   |                         | μA    |

| Power Consumption                             |                                                                                |                          | 215   |                         | mW    |

| AVDD Supply Current (I <sub>AVDD</sub> )      |                                                                                |                          | 2.5   |                         |       |

| AVCC Supply Current (I <sub>AVCC</sub> )      |                                                                                |                          | 1     |                         |       |

| AVSS Supply Current (I <sub>AVSS</sub> )      | 1                                                                              |                          | -3    |                         | mA    |

| AVEE Supply Current (I <sub>AVEE</sub> )      | Power-down mode                                                                |                          | -1.75 |                         |       |

| DVDD Supply Current (I <sub>DVDD</sub> )      | 1                                                                              |                          | 0.75  |                         |       |

| IOVDD Supply Current (I <sub>IODD</sub> )     | 1                                                                              |                          | 1.5   |                         | μA    |

| Power Consumption                             | 1                                                                              |                          | 90    |                         | mW    |

### **TIMING REQUIREMENTS**

$(V_{AVDD} = V_{DVDD} = 4.7V \text{ to } 5.5V, V_{AVCC} = 12V, V_{AVEE} = -12V, AGND = DGND = V_{AVSSB} = V_{AVSSC} = V_{AVSSD} = 0V, DAC \text{ output range} = 0V \text{ to } 10V \text{ for all groups, no load on the DACs, } T_A = -40^{\circ}C \text{ to } +105^{\circ}C, \text{ unless otherwise noted})$

| PARAMETER                                                                                              | CONDITIONS                        | MIN   | TYP | MAX | UNITS |  |

|--------------------------------------------------------------------------------------------------------|-----------------------------------|-------|-----|-----|-------|--|

| Serial Interface <sup>(1)</sup>                                                                        |                                   |       |     |     |       |  |

| 001// 5 // )                                                                                           | $V_{IOVDD}$ = 1.8V to 2.7V        |       |     | 15  |       |  |

| SCLK Frequency (f <sub>SCLK</sub> )                                                                    | V <sub>IOVDD</sub> = 2.7 to 5.25V |       |     | 20  | MHz   |  |

|                                                                                                        | $V_{IOVDD}$ = 1.8V to 2.7V        | 66.67 |     |     |       |  |

| SCLK Period (t <sub>P</sub> )                                                                          | V <sub>IOVDD</sub> = 2.7 to 5.25V | 50    |     |     | ns    |  |

|                                                                                                        | $V_{IOVDD}$ = 1.8V to 2.7V        | 30    |     |     |       |  |

| SCLK Pulse Width High (t <sub>PH</sub> )                                                               | V <sub>IOVDD</sub> = 2.7 to 5.25V | 23    |     |     | ns    |  |

|                                                                                                        | $V_{IOVDD}$ = 1.8V to 2.7V        | 30    |     |     |       |  |

| SCLK Pulse Width Low (t <sub>PL</sub> )                                                                | V <sub>IOVDD</sub> = 2.7 to 5.25V | 23    |     |     | ns    |  |

|                                                                                                        | $V_{IOVDD}$ = 1.8V to 2.7V        | 10    |     |     |       |  |

| SDI Setup (t <sub>SU</sub> )                                                                           | V <sub>IOVDD</sub> = 2.7 to 5.25V | 10    |     |     | ns    |  |

| 001111114                                                                                              | $V_{IOVDD}$ = 1.8V to 2.7V        | 10    |     |     | — ns  |  |

| SDI Hold (t <sub>H</sub> )                                                                             | V <sub>IOVDD</sub> = 2.7 to 5.25V | 10    |     |     |       |  |

| $ODO$ Drivers To Tot $Otata \begin{pmatrix} 2 \\ 2 \end{pmatrix} \begin{pmatrix} 4 \\ - \end{pmatrix}$ | $V_{IOVDD}$ = 1.8V to 2.7V        | 0     |     | 15  |       |  |

| SDO Driven To Tri- State $^{(2)}$ (t <sub>ODZ</sub> )                                                  | V <sub>IOVDD</sub> = 2.7 to 5.25V | 0     |     | 9   | ns    |  |

| $ODO$ Tri Otata Ta Driver $\binom{2}{4}$ (t. )                                                         | $V_{IOVDD}$ = 1.8V to 2.7V        | 0     |     | 23  | ns    |  |

| SDO Tri-State To Driven $^{(2)}(t_{OZD})$                                                              | V <sub>IOVDD</sub> = 2.7 to 5.25V | 0     |     | 15  |       |  |

| ODO Output Delev <sup>(2)</sup> (t. )                                                                  | $V_{IOVDD} = 1.8V$ to 2.7V        | 0     |     | 23  |       |  |

| SDO Output Delay $^{(2)}(t_{OD})$                                                                      | V <sub>IOVDD</sub> = 2.7 to 5.25V | 0     |     | 15  | ns    |  |

|                                                                                                        | $V_{IOVDD}$ = 1.8V to 2.7V        | 5     |     |     |       |  |

| nCS Setup (t <sub>SU_nCS</sub> )                                                                       | V <sub>IOVDD</sub> = 2.7 to 5.25V | 5     |     |     | ns    |  |

|                                                                                                        | $V_{IOVDD}$ = 1.8V to 2.7V        | 20    |     |     |       |  |

| nCS Hold (t <sub>H_nCS</sub> )                                                                         | V <sub>IOVDD</sub> = 2.7 to 5.25V | 20    |     |     | ns    |  |

|                                                                                                        | $V_{IOVDD}$ = 1.8V to 2.7V        | 10    |     |     |       |  |

| Inter-Access Gap (t <sub>IAG</sub> )                                                                   | V <sub>IOVDD</sub> = 2.7 to 5.25V | 10    |     |     | ns    |  |

| Digital Logic                                                                                          |                                   |       |     |     | •     |  |

| Reset Delay; Delay-to-Normal Operation from Reset                                                      |                                   |       | 100 |     | μs    |  |

| Power-Down Recovery Time                                                                               |                                   |       |     | 70  | μs    |  |

| Clamp Shutdown Delay                                                                                   |                                   |       | 100 |     | μs    |  |

| Convert Pulse Width                                                                                    |                                   | 20    |     |     | ns    |  |

| Reset Pulse Width                                                                                      |                                   | 20    |     |     | ns    |  |

| ADC WAIT State <sup>(3)</sup> ; the Wait Time from When the ADC Enters the IDLE State                  |                                   | 2     |     |     | μs    |  |

NOTES:

1. Specified by design and characterization. Not tested during production.

2. SDO loaded with 10 pF load capacitance for SDO timing specifications.

3. Specified by design; not subject to production testing. See the ADC Sequencing section for more details.

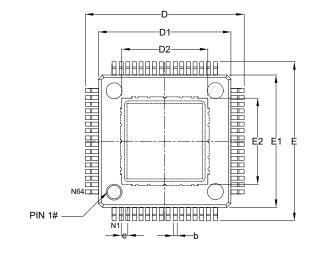

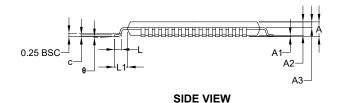

## PACKAGE OUTLINE DIMENSIONS

## TQFP-10×10-64L (Exposed Pad)

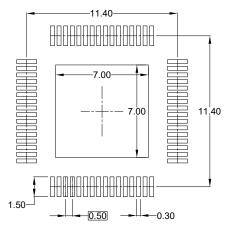

RECOMMENDED LAND PATTERN (Unit: mm)

| Ourseland | Dimensions In Millimeters |           |        |  |  |  |

|-----------|---------------------------|-----------|--------|--|--|--|

| Symbol    | MIN                       | MOD       | MAX    |  |  |  |

| А         | -                         | -         | 1.200  |  |  |  |

| A1        | 0.050                     | -         | 0.150  |  |  |  |

| A2        | 0.950                     | 1.000     | 1.050  |  |  |  |

| A3        | 0.390                     | 0.440     | 0.490  |  |  |  |

| b         | 0.170                     | -         | 0.270  |  |  |  |

| С         | 0.090                     | 0.130     | 0.180  |  |  |  |

| D         | 11.800                    | 12.000    | 12.200 |  |  |  |

| D1        | 9.900                     | 10.000    | 10.100 |  |  |  |

| D2        | 5.900                     | -         | 6.800  |  |  |  |

| E         | 11.800                    | 12.000    | 12.200 |  |  |  |

| E1        | 9.900                     | 10.000    | 10.100 |  |  |  |

| E2        | 5.900                     | -         | 6.800  |  |  |  |

| е         | 0.400                     | 0.500     | 0.600  |  |  |  |

| L         | 0.450                     | -         | 0.750  |  |  |  |

| L1        |                           | 1.000 REF |        |  |  |  |

| θ         | 0°                        | 3.5°      | 7°     |  |  |  |

NOTES:

1. Body dimensions do not include mode flash or protrusion.

2. This drawing is subject to change without notice.