# REF4132-Q1 Low-Drift, Low-Power, Small-Footprint Series Voltage Reference

### **Features**

- Qualified for automotive applications

- AEC-Q100 qualified with the following results:

- Device temperature grade 1: –40°C to +125°C ambient operating temperature range

- Device HBM ESD classification level 2

- Voltage options: 2.5V, 3V, 3.3V, 4.096V, 5V

- Initial accuracy: ±0.05% (maximum)

- Temperature coefficient : A grade: 12 ppm/°C (maximum) B grade: 30 ppm/°C (maximum)

- Operating temperature range: -40°C to +125°C

- Output current: ±10 mA

- Low guiescent current: 100 µA (maximum)

- Output 1/f noise (0.1 Hz to 10 Hz): 15  $\mu$ V<sub>PP</sub>/V

- Excellent long-term stability 30 ppm/1000 hrs

- Small footprint 5-pin SOT-23 package

# **Applications**

- ADAS front camera

- ADAS surround view system ECU

- Traction inverter

- Automotive DC/DC converter

- HEV/EV On-board (OBC) & wireless charger

### 3 Description

The REF4132-Q1 device is a low temperature drift (12 ppm/°C), low-power, high-precision CMOS voltage reference, featuring ±0.05% initial accuracy, low operating current with power consumption less than 100µA. This device also offers very low output noise of 15  $\mu V_{p-p}$  /V, which enables its ability to maintain high signal integrity with high-resolution data converters in noise critical systems. Packaged in the SOT-23-5 package. REF4132-Q1 offers enhanced specifications and pin-to-pin replacement for LM4128-Q1 and LM4132-Q1.

Stability and system reliability are further improved by the low output-voltage hysteresis of the device and low long-term output voltage drift. Furthermore, the small size and low operating current of the devices (100 μA) can benefit portable and battery-powered applications.

REF4132-Q1 is specified for the wide temperature range of -40°C to +125°C.

### Device Information<sup>(1)</sup>

| PART NAME  | PACKAGE    | BODY SIZE (NOM)   |

|------------|------------|-------------------|

| REF4132-Q1 | SOT-23 (5) | 2.90 mm × 1.60 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

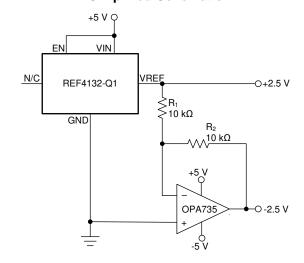

# Simplified Schematic

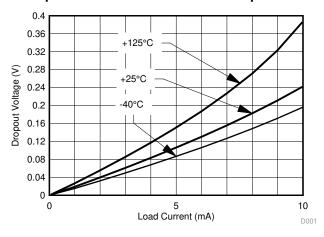

### **Dropout vs. Current Load Over Temperature**

# **Table of Contents**

| 1 | Features 1                           |    | 9.1 Overview                                                 | 13    |

|---|--------------------------------------|----|--------------------------------------------------------------|-------|

| 2 | Applications 1                       |    | 9.2 Functional Block Diagram                                 | 13    |

| 3 | Description 1                        |    | 9.3 Feature Description                                      | 13    |

| 4 | Revision History2                    |    | 9.4 Device Functional Modes                                  | 14    |

| 5 | Device Comparison Table              | 10 | Application and Implementation                               |       |

| 6 | Pin Configuration and Functions3     |    | 10.1 Application Information                                 | 15    |

| 7 | Specifications                       |    | 10.2 Typical Application: Basic Voltage Reference Connection | 15    |

|   | 7.1 Absolute Maximum Ratings         |    | Power Supply Recommendations                                 | 17    |

|   | 7.3 Recommended Operating Conditions | 12 | Layout                                                       | 17    |

|   | 7.4 Thermal Information              |    | 12.1 Layout Guidelines                                       | 17    |

|   | 7.5 Electrical Characteristics 5     |    | 12.2 Layout Example                                          | 17    |

|   |                                      | 13 | Device and Documentation Support                             | 18    |

| _ | 7.6 Typical Characteristics          |    | 13.1 Documentation Support                                   | 18    |

| 8 | Parameter Measurement Information 10 |    | 13.2 Receiving Notification of Documentation Update          | es 18 |

|   | 8.1 Solder Heat Shift                |    | 13.3 Support Resources                                       | 18    |

|   | 8.2 Long-Term Stability              |    | 13.4 Trademarks                                              |       |

|   | 8.3 Thermal Hysteresis               |    | 13.5 Electrostatic Discharge Caution                         | 18    |

|   | 8.4 Power Dissipation                |    | 13.6 Glossary                                                |       |

|   | 8.5 Noise Performance                | 14 | Mechanical, Packaging, and Orderable                         |       |

| 9 | Detailed Description                 |    | Information                                                  | 18    |

|   |                                      |    |                                                              |       |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cł | hanges from Original (February 2020) to Revision A | Page |

|----|----------------------------------------------------|------|

| •  | APL to RTM release.                                | 1    |

# 5 Device Comparison Table

| PRODUCT       | V <sub>OUT</sub> |

|---------------|------------------|

| REF4132 - 2.5 | 2.5 V            |

| REF4132 - 3.0 | 3 V              |

| REF4132 - 3.3 | 3.3 V            |

| REF4132 - 4.0 | 4.096 V          |

| REF4132 - 5.0 | 5 V              |

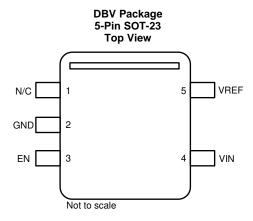

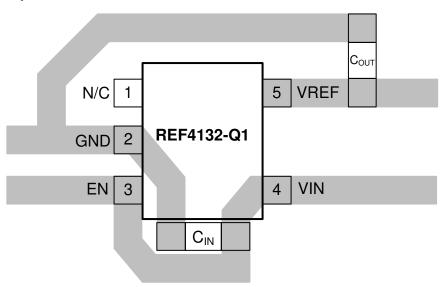

# 6 Pin Configuration and Functions

# **Pin Functions**

| PIN |      | TYPE   | DESCRIPTION                                 |  |  |  |

|-----|------|--------|---------------------------------------------|--|--|--|

| NO. | NAME | ITPE   | DESCRIPTION                                 |  |  |  |

| 1   | N/C  | _      | No connect pin, leave floating              |  |  |  |

| 2   | GND  | Ground | Ground                                      |  |  |  |

| 3   | EN   | I/O    | Enable pin. Enables or disables the device. |  |  |  |

| 4   | VIN  | Power  | Input supply                                |  |  |  |

| 5   | VREF | Output | Reference output                            |  |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                              |                 | MIN  | MAX            | UNIT |

|------------------------------|-----------------|------|----------------|------|

| Input voltage                | V <sub>IN</sub> | -0.3 | 6              | V    |

| Enable voltage               | V <sub>EN</sub> | -0.3 | $V_{IN} + 0.3$ | V    |

| Output voltage               | $V_{REF}$       | -0.3 | 5.5            | V    |

| Output short circuit current | I <sub>SC</sub> |      | 20             | mA   |

| Operating temperature range  | T <sub>A</sub>  | -55  | 150            | °C   |

| Storage temperature range    | Tstg            | -65  | 170            | °C   |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied. These are stress ratings only and functional operation of the device at these or any other conditions beyond those specified in the Electrical Characteristics Table is not implied.

# 7.2 ESD Ratings

|                    |                         |                                                         | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------|------|

| V                  | Electrostatio discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2500 | .,   |

| V <sub>(ESD)</sub> |                         | Charged-device model (CDM), per AEC Q100-011            | ±1500 | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                       | MIN                                               | NOM | MAX      | UNIT |

|-----------------|-----------------------|---------------------------------------------------|-----|----------|------|

| V <sub>IN</sub> | Input Voltage         | V <sub>REF</sub> + V <sub>DO</sub> <sup>(1)</sup> |     | 5.5      | V    |

| $V_{EN}$        | Enable Voltage        | 0                                                 |     | $V_{IN}$ | V    |

| IL              | Output Current        | -10                                               |     | 10       | mA   |

| T <sub>A</sub>  | Operating Temperature | -40                                               | 25  | 125      | °C   |

<sup>(1)</sup> Dropout voltage

### 7.4 Thermal Information

|                      |                                              | DEVICE |      |

|----------------------|----------------------------------------------|--------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DBV    | UNIT |

|                      |                                              | 5 PINS |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 185    | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 156    | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 29.6   | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 33.8   | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter | 29.1   | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A    | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

At  $V_{IN}$  = 5.5 V,  $V_{EN}$  =  $V_{IN}$ ,  $C_{REF}$  = 10  $\mu F$ ,  $C_{IN}$  = 0.1  $\mu F$ ,  $I_L$  = 0 mA, minimum and maximum specifications at  $T_A$  =  $-40^{\circ}C$  to 125°C; typical specifications at  $T_A$  = 25°C unless otherwise noted

| PARAMETER                      |                               | TEST CO                                     | MIN                                    | TYP                                | MAX | UNIT |                    |

|--------------------------------|-------------------------------|---------------------------------------------|----------------------------------------|------------------------------------|-----|------|--------------------|

| ACCURACY AND                   | DRIFT                         |                                             |                                        |                                    |     |      |                    |

|                                | Output voltage accuracy       | T <sub>A</sub> = 25°C                       |                                        | -0.05                              |     | 0.05 | %                  |

|                                | Output voltage                | –40°C ≤ T <sub>A</sub> ≤ 125°C              | REF4132 A grade                        |                                    |     | 12   | ppm/°C             |

|                                | temperature coefficient       | $-40$ °C $\leq$ T <sub>A</sub> $\leq$ 125°C | REF4132 B grade                        |                                    |     | 30   | ppm/°C             |

| LINE & LOAD RE                 | GULATION                      |                                             |                                        |                                    |     |      |                    |

|                                |                               | $V_{REF} + V_{DO} \le V_{IN} \le 5.5$       | 5 V                                    |                                    | 2   |      | ppm/V              |

| $\Delta V_{REF}/\Delta V_{IN}$ | Line Regulation               | $V_{REF} + V_{DO} \le V_{IN} \le 5.5$       | 5 V                                    |                                    |     | 15   | ppm/V              |

|                                |                               | $V_{REF} = 5 \text{ V}, V_{REF} + V_{D}$    | <sub>O</sub> ≤ V <sub>IN</sub> ≤ 5.5 V |                                    |     | 55   | ppm/V              |

| A)/ /AI                        | Load Degulation               | $I_L = 0$ mA to 10mA, $V_{IN}$              | $V_{REF} + V_{DO}$                     |                                    | 20  |      | ppm/mA             |

| $\Delta V_{REF}/\Delta I_{L}$  | Load Regulation               | $I_L = 0$ mA to 10mA, $V_{IN}$              | N = V <sub>REF</sub> + V <sub>DO</sub> |                                    |     | 120  | ppm/mA             |

| POWER SUPPLY                   | ,                             |                                             |                                        |                                    |     |      |                    |

| V <sub>IN</sub>                | Input voltage                 |                                             |                                        | V <sub>REF</sub> + V <sub>DO</sub> |     | 5.5  | ٧                  |

|                                | 0                             | Active mode                                 |                                        | 80                                 | 100 | μA   |                    |

| IQ                             | Quiescent current             | Shutdown mode, V <sub>EN</sub> :            | = 0 V                                  |                                    | 2.5 | 5    | μA                 |

| V Enable pin                   |                               | Voltage reference in a                      | ctive mode (EN=1)                      | 1.6                                |     |      | V                  |

| V <sub>EN</sub>                | Voltage                       | Voltage reference in sl                     | hutdown mode (EN=0)                    |                                    |     | 0.5  | V                  |

| I <sub>EN</sub>                | Enable pin current            | V <sub>EN</sub> = 5.5 V                     |                                        |                                    | 1   | 2    | μΑ                 |

|                                |                               | $I_L = 0 \text{ mA}$                        |                                        |                                    | 50  |      | mV                 |

| $V_{DO}$                       | Dropout voltage               | $I_L = 0 \text{ mA}$                        |                                        |                                    | 100 | mV   |                    |

|                                |                               | $I_L = 10 \text{ mA}$                       |                                        |                                    |     | 500  | mV                 |

| I <sub>SC</sub>                | Short circuit current         | V <sub>REF</sub> = 0 V                      |                                        |                                    | 18  | 11.5 | mA                 |

| TURNON                         |                               | -                                           |                                        |                                    |     | ·    |                    |

| t <sub>ON</sub>                | Turn-on time                  | 0.1% settling, $C_L = 1 \mu$                | F, 10% to 90%                          |                                    | 2.5 |      | ms                 |

| NOISE                          |                               |                                             |                                        |                                    |     |      |                    |

| e <sub>n(p-p)</sub>            | Low frequency noise           | f = 0.1 Hz to 10 Hz                         |                                        |                                    | 15  |      | ppm <sub>p-p</sub> |

| e <sub>n</sub>                 | Wide band noise               | f = 10 Hz to 10 kHz                         |                                        |                                    | 24  |      | $\mu V_{rms}$      |

| HYSTERESIS AN                  | ID LONG-TERM STABILITY        | ,                                           |                                        |                                    |     |      |                    |

|                                | Long-term stability           | 0 to 1000h at 35°C                          |                                        |                                    | 30  |      | ppm                |

| V <sub>HYST</sub>              | Output voltage hysteresis     | T <sub>A</sub> = 25°C to -40°C to 1         |                                        | 35                                 |     | ppm  |                    |

| CAPACITIVE LO                  | AD                            |                                             |                                        |                                    |     |      |                    |

| C <sub>L</sub>                 | Stable output capacitor range |                                             |                                        | 0.1                                |     | 10   | μF                 |

|                                |                               | 1                                           |                                        |                                    |     |      |                    |

<sup>(1)</sup> At higher ambient temperature the short circuit current capacity is limited due to junction temperature max limit

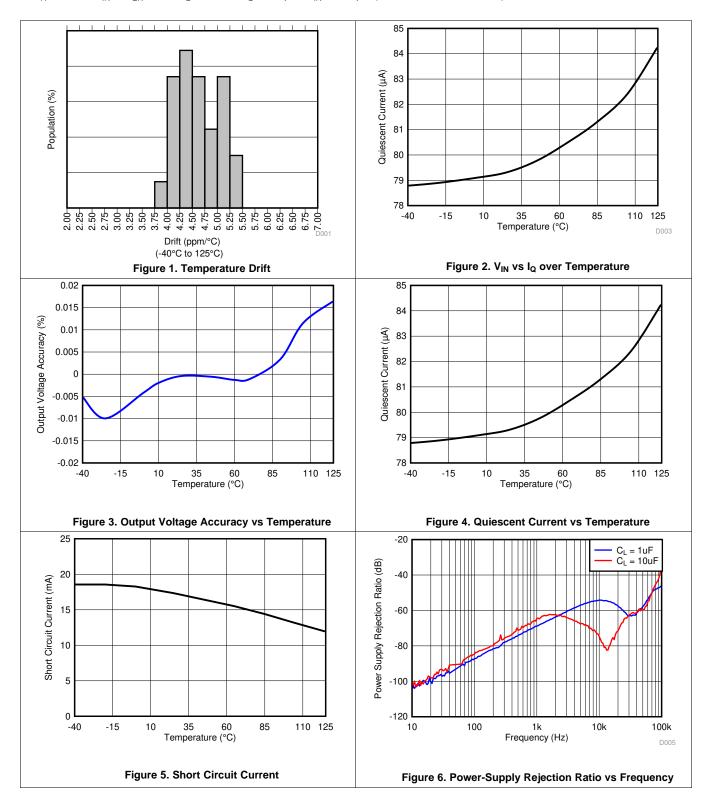

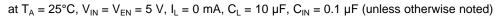

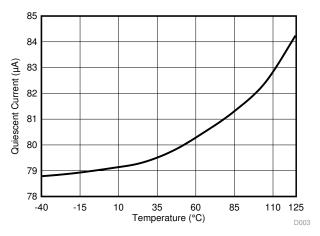

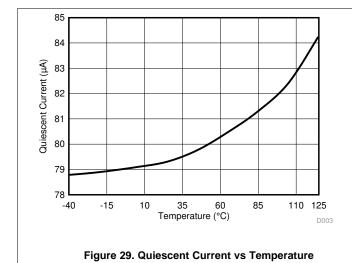

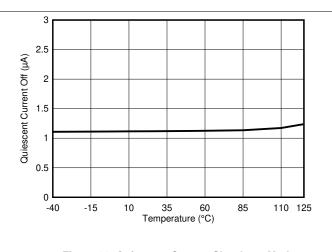

### 7.6 Typical Characteristics

at  $T_A$  = 25°C,  $V_{IN}$  =  $V_{EN}$  = 5 V,  $I_L$  = 0 mA,  $C_L$  = 10  $\mu$ F,  $C_{IN}$  = 0.1  $\mu$ F (unless otherwise noted)

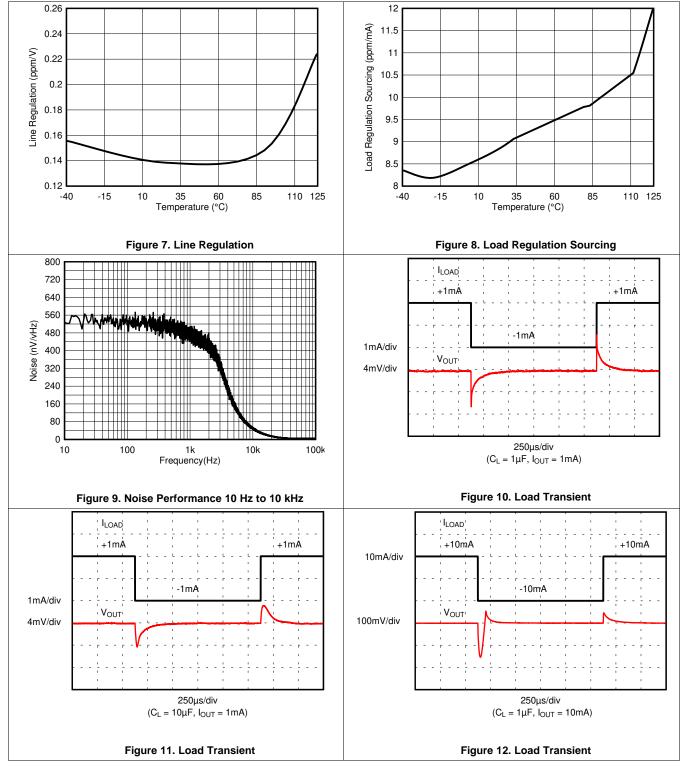

# **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C,  $V_{IN} = V_{EN} = 5$  V,  $I_L = 0$  mA,  $C_L = 10$   $\mu$ F,  $C_{IN} = 0.1$   $\mu$ F (unless otherwise noted)

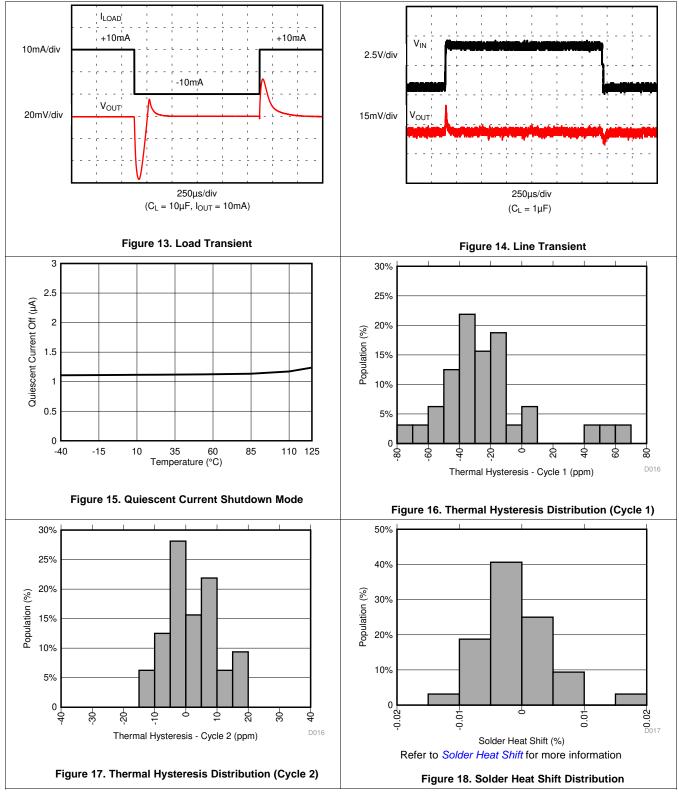

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C,  $V_{IN} = V_{EN} = 5$  V,  $I_L = 0$  mA,  $C_L = 10$   $\mu$ F,  $C_{IN} = 0.1$   $\mu$ F (unless otherwise noted)

### 8 Parameter Measurement Information

### 8.1 Solder Heat Shift

The materials used in the manufacture of the REF4132-Q1 have differing coefficients of thermal expansion, resulting in stress on the device die when the part is heated. Mechanical and thermal stress on the device die can cause the output voltages to shift, degrading the initial accuracy specifications of the product. Reflow soldering is a common cause of this error.

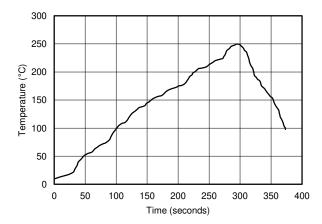

In order to illustrate this effect, a total of 32 devices were soldered on four printed circuit boards [16 devices on each printed circuit board (PCB)] using lead-free solder paste and the paste manufacturer suggested reflow profile. The reflow profile is as shown in Figure 21. The printed circuit board is comprised of FR4 material. The board thickness is 1.65 mm and the area is 114 mm × 152 mm.

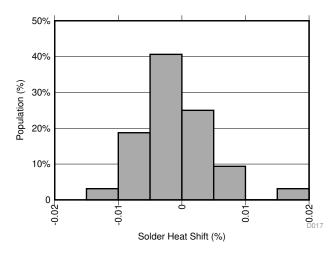

Figure 21. Reflow Profile

The reference output voltage is measured before and after the reflow process; the typical shift is displayed in Figure 22 Although all tested units exhibit very low shifts (< 0.01%), higher shifts are also possible depending on the size, thickness, and material of the printed circuit board. An important note is that the histograms display the typical shift for exposure to a single reflow profile. Exposure to multiple reflows, as is common on PCBs with surface-mount components on both sides, causes additional shifts in the output bias voltage. If the PCB is exposed to multiple reflows, the device must be soldered in the second pass to minimize its exposure to thermal stress.

Figure 22. Solder Heat Shift Distribution, V<sub>REF</sub> (%)

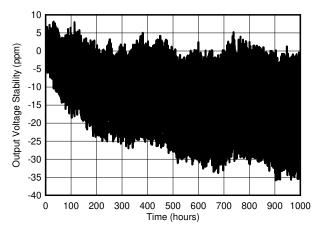

### 8.2 Long-Term Stability

One of the key parameters of the REF4132-Q1 references is long-term stability. Typical characteristic expressed as: curves shows the typical drift value for the REF4132-Q1 is 25 ppm from 0 to 1000 hours. This parameter is characterized by measuring 32 units at regular intervals for a period of 1000 hours. It is important to understand that long-term stability is not ensured by design and that the output from the device may shift beyond the typical 25 ppm specification at any time. For systems that require highly stable output voltages over long periods of time, the designer should consider burning in the devices prior to use to minimize the amount of output drift exhibited by the reference over time.

Figure 23. Long Term Stability - 1000 hours (V<sub>REF</sub>)

### 8.3 Thermal Hysteresis

Thermal hysteresis is measured with the REF4132-Q1 soldered to a PCB, similar to a real-world application. Thermal hysteresis for the device is defined as the change in output voltage after operating the device at 25°C, cycling the device through the specified temperature range, and returning to 25°C. The PCB was baked at 150°C for 30 minutes before thermal hysteresis was measured. Hysteresis can be expressed by Equation 1:

$$V_{HYST} = \left(\frac{|V_{PRE} - V_{POST}|}{V_{NOM}}\right) \times 10^6 \text{ (ppm)}$$

### where

- V<sub>HYST</sub> = thermal hysteresis (in units of ppm)

- V<sub>NOM</sub> = the specified output voltage

- V<sub>PRE</sub> = output voltage measured at 25°C pre-temperature cycling

- V<sub>POST</sub> = output voltage measured after the device has cycled from 25°C through the specified temperature range of –40°C to +125°C and returns to 25°C.

Figure 24. Thermal Hysteresis Distribution (V<sub>REF</sub>)

### 8.4 Power Dissipation

The REF4132-Q1 voltage references are capable of source and sink up to 10 mA of load current across the rated input voltage range. However, when used in applications subject to high ambient temperatures, the input voltage and load current must be carefully monitored to ensure that the device does not exceeded its maximum power dissipation rating. The maximum power dissipation of the device can be calculated with Equation 2:

$$T_J = T_A + P_D \times R_{\theta JA}$$

where

- P<sub>D</sub> is the device power dissipation

- T<sub>J</sub> is the device junction temperature

- T<sub>A</sub> is the ambient temperature

- R<sub>θJA</sub> is the package (junction-to-air) thermal resistance

(2)

Because of this relationship, acceptable load current in high temperature conditions may be less than the maximum current-sourcing capability of the device. In no case should the device be operated outside of its maximum power rating because doing so can result in premature failure or permanent damage to the device.

### 8.5 Noise Performance

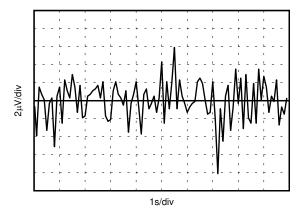

Typical 0.1-Hz to 10-Hz voltage noise can be seen in Figure 25. Device noise increases with output voltage and operating temperature. Additional filtering can be used to improve output noise levels, although care must be taken to ensure the output impedance does not degrade ac performance. Peak-to-peak noise measurement setup is shown in Figure 25.

Figure 25. 0.1-Hz to 10-Hz Noise (V<sub>REF</sub>)

### 9 Detailed Description

#### 9.1 Overview

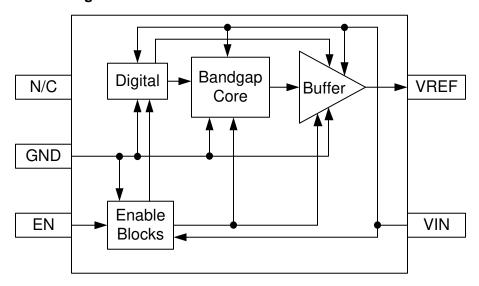

The REF4132-Q1 is a low-drift, low-power precision bandgap voltage reference that is specifically designed for excellent initial voltage accuracy and drift. The *Functional Block Diagram* is a simplified block diagram of the REF4132-Q1 showing basic band-gap topology.

### 9.2 Functional Block Diagram

# 9.3 Feature Description

# 9.3.1 Supply Voltage

The REF4132-Q1 voltage reference features an extremely low dropout voltage. For loaded conditions, a typical dropout voltage versus load is shown on the front page. The REF4132-Q1 features a low quiescent current that is extremely stable over changes in both temperature and supply. The typical room temperature quiescent current is 75  $\mu$ A, and the maximum quiescent current over temperature is just 100  $\mu$ A. Supply voltages below the specified levels can cause the REF4132-Q1 to momentarily draw currents greater than the typical quiescent current. Use a power supply with a fast rising edge and low output impedance to easily prevent this issue.

The supply current vs supply voltage figure is shown in Figure 26.

Figure 26. Supply Current vs Supply Voltage

### Feature Description (continued)

#### 9.3.2 Low Temperature Drift

The REF4132-Q1 is designed for minimal drift error, which is defined as the change in output voltage over temperature. The drift is calculated using the box method, as described by Equation 3:

$$Drift = \left(\frac{V_{REF(MAX)} - V_{REF(MIN)}}{V_{REF} \times Temperature Range}\right) \times 10^{6}$$

(3)

### 9.3.3 Load Current

The REF4132-Q1 family is specified to deliver a current load of  $\pm 10$  mA per output. The V<sub>REF</sub> output of the device are protected from short circuits by limiting the output short-circuit current to 18 mA. The device temperature increases according to Equation 4:

$$T_J T_A + P_D \times R_{\theta JA}$$

where

- T<sub>.1</sub> = junction temperature (°C),

- T<sub>A</sub> = ambient temperature (°C),

- P<sub>D</sub> = power dissipated (W), and

- R<sub>BJA</sub> = junction-to-ambient thermal resistance (°C/W) (4)

The REF4132-Q1 maximum junction temperature must not exceed the absolute maximum rating of 150°C.

### 9.4 Device Functional Modes

#### 9.4.1 EN Pin

When the EN pin of the REF4132-Q1 is pulled high, the device is in active mode. The device must be in active mode for normal operation. The REF4132-Q1 can be placed in a low-power mode by pulling the ENABLE pin low. When in shutdown mode, the output of the device becomes high impedance and the quiescent current of the device reduces to 2.5 µA (typical) in shutdown mode. The EN pin must not be pulled higher than VIN supply voltage. See the Thermal Information for logic high and logic low voltage levels.

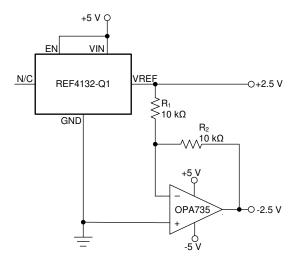

### 9.4.2 Negative Reference Voltage

For applications requiring a negative and positive reference voltage, the REF4132-Q1 and OPA735 can be used to provide a dual-supply reference from a 5-V supply. Figure 27 shows the REF4132-Q1 used to provide a 2.5-V supply reference voltage. The low drift performance of the REF4132-Q1 complements the low offset voltage and zero drift of the OPA735 to provide an accurate solution for split-supply applications. Take care to match the temperature coefficients of R1 and R2.

Figure 27. REF4132-Q1 and OPA735 Create Positive and Negative Reference Voltages

# 10 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 10.1 Application Information

Traction Inverter

Automotive Head Unit

As this device has many applications and setups, there are many situations that this datasheet can not characterize in detail. Basic applications includes positive/negative voltage reference and data acquisition systems. The table below shows the typical application of REF4132-Q1 and its companion ADC.

Applications

ADC/DAC

HEV/EV

ADS1259-Q1, ADS1015-Q1, ADS7049-Q1

High Temperature Sensor

ADS1118-Q1

**Table 1. Typical Applications and Companion ADC**

ADS7049-Q1

ADS7142-Q1

# 10.2 Typical Application: Basic Voltage Reference Connection

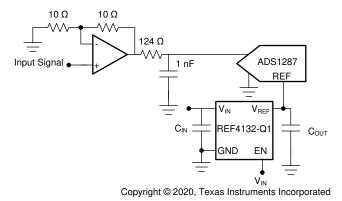

The circuit shown in Figure 28 shows the basic configuration for the REF4132-Q1 references. Connect bypass capacitors according to the guidelines in *Layout Guidelines*.

Figure 28. Basic Reference Connection

### 10.2.1 Design Requirements

A detailed design procedure is described based on a design example. For this design example, use the parameters listed in Table 2 as the input parameters.

| DESIGN PARAMETER                | VALUE |

|---------------------------------|-------|

| Input voltage V <sub>IN</sub>   | 5 V   |

| Output voltage V <sub>OUT</sub> | 2.5 V |

| REF4132-Q1 input capacitor      | 1 μF  |

| REF4132-Q1 output capacitor     | 10 μF |

**Table 2. Design Example Parameters**

### 10.2.2 Detailed Design Procedure

### 10.2.2.1 Input and Output Capacitors

A 1- $\mu$ F to 10- $\mu$ F electrolytic or ceramic capacitor can be connected to the input to improve transient response in applications where the supply voltage may fluctuate. Connect an additional 0.1- $\mu$ F ceramic capacitor in parallel to reduce high frequency supply noise.

A ceramic capacitor of at least a  $0.1~\mu F$  must be connected to the output to improve stability and help filter out high frequency noise. An additional  $1-\mu F$  to  $10-\mu F$  electrolytic or ceramic capacitor can be added in parallel to improve transient performance in response to sudden changes in load current; however, keep in mind that doing so increases the turnon time of the device.

Best performance and stability is attained with low-ESR, low-inductance ceramic chip-type output capacitors (X5R, X7R, or similar). If using an electrolytic capacitor on the output, place a 0.1-μF ceramic capacitor in parallel to reduce overall ESR on the output.

### 10.2.2.2 V<sub>IN</sub> Slew Rate Considerations

In applications with slow-rising input voltage signals, the reference exhibits overshoot or other transient anomalies that appear on the output. These phenomena also appear during shutdown as the internal circuitry loses power.

To avoid such conditions, ensure that the input voltage wave-form has both a rising and falling slew rate close to 6 V/ms.

#### 10.2.2.3 Shutdown/Enable Feature

The REF4132-Q1 references can be switched to a low power shut-down mode when a voltage of 0.5 V or lower is input to the ENABLE pin. Likewise, the reference becomes operational for ENABLE voltages of 1.6 V or higher. During shutdown, the supply current drops to less than 5  $\mu$ A, useful in applications that are sensitive to power consumption.

If using the shutdown feature, ensure that the ENABLE pin voltage does not fall between 0.5 V and 1.6 V because this causes a large increase in the supply current of the device and may keep the reference from starting up correctly. If not using the shutdown feature, however, the ENABLE pin can simply be tied to the IN pin, and the reference remains operational continuously.

### 10.2.3 Application Curves

Figure 30. Quiescent Current Shutdown Mode

# 11 Power Supply Recommendations

The REF4132-Q1 family of references feature an extremely low-dropout voltage. These references can be operated with a supply of only 50 mV above the output voltage. TI recommends a supply bypass capacitor ranging between 0.1  $\mu$ F to 10  $\mu$ F.

### 12 Layout

### 12.1 Layout Guidelines

Figure 31 illustrates an example of a PCB layout for a data acquisition system using the REF4132-Q1. Some key considerations are:

- Connect low-ESR,  $0.1-\mu F$  ceramic bypass capacitors at  $V_{IN}$ ,  $V_{REF}$  of the REF4132-Q1.

- Decouple other active devices in the system per the device specifications.

- Using a solid ground plane helps distribute heat and reduces electromagnetic interference (EMI) noise pickup.

- Place the external components as close to the device as possible. This configuration prevents parasitic errors (such as the Seebeck effect) from occurring.

- Do not run sensitive analog traces in parallel with digital traces. Avoid crossing digital and analog traces if possible, and only make perpendicular crossings when absolutely necessary.

### 12.2 Layout Example

Figure 31. Layout Example

# 13 Device and Documentation Support

### 13.1 Documentation Support

#### 13.1.1 Related Documentation

For related documentation see the following:

- INA21x Voltage Output, Low- or High-Side Measurement, Bidirectional, Zero-Drift Series, Current-Shunt Monitors

- Low-Drift Bidirectional Single-Supply Low-Side Current Sensing Reference Design

# 13.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### 13.3 Support Resources

TI E2E™ support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 13.4 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

# 13.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 13.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 14 Mechanical, Packaging, and Orderable Information

The following pages include mechanical packaging and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                     |              |                      |         |

| REF4132A25DBVRQ1 | ACTIVE | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 25MC                 | Samples |

| REF4132A30DBVRQ1 | ACTIVE | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 25NC                 | Samples |

| REF4132A33DBVRQ1 | ACTIVE | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 25OC                 | Samples |

| REF4132A40DBVRQ1 | ACTIVE | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 25PC                 | Samples |

| REF4132A50DBVRQ1 | ACTIVE | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 25QC                 | Samples |

| REF4132B25DBVRQ1 | ACTIVE | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 25XC                 | Samples |

| REF4132B30DBVRQ1 | ACTIVE | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 25RC                 | Samples |

| REF4132B33DBVRQ1 | ACTIVE | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 25SC                 | Samples |

| REF4132B40DBVRQ1 | ACTIVE | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 25TC                 | Samples |

| REF4132B50DBVRQ1 | ACTIVE | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 25VC                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet J\$709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

# PACKAGE OPTION ADDENDUM

27-Aug-2021

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF REF4132-Q1:

Catalog: REF4132

NOTE: Qualified Version Definitions:

Catalog - TI's standard catalog product

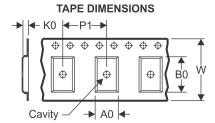

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

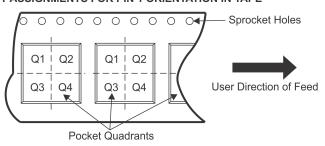

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| REF4132A25DBVRQ1 | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

| REF4132A30DBVRQ1 | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

| REF4132A33DBVRQ1 | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

| REF4132A40DBVRQ1 | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

| REF4132A50DBVRQ1 | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

| REF4132B25DBVRQ1 | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

| REF4132B30DBVRQ1 | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

| REF4132B33DBVRQ1 | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

| REF4132B40DBVRQ1 | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

| REF4132B50DBVRQ1 | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

\*All dimensions are nominal

| All differsions are normal |              |                 |      |      |             |            |             |  |  |

|----------------------------|--------------|-----------------|------|------|-------------|------------|-------------|--|--|

| Device                     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |  |

| REF4132A25DBVRQ1           | SOT-23       | DBV             | 5    | 3000 | 213.0       | 191.0      | 35.0        |  |  |

| REF4132A30DBVRQ1           | SOT-23       | DBV             | 5    | 3000 | 213.0       | 191.0      | 35.0        |  |  |

| REF4132A33DBVRQ1           | SOT-23       | DBV             | 5    | 3000 | 213.0       | 191.0      | 35.0        |  |  |

| REF4132A40DBVRQ1           | SOT-23       | DBV             | 5    | 3000 | 213.0       | 191.0      | 35.0        |  |  |

| REF4132A50DBVRQ1           | SOT-23       | DBV             | 5    | 3000 | 213.0       | 191.0      | 35.0        |  |  |

| REF4132B25DBVRQ1           | SOT-23       | DBV             | 5    | 3000 | 213.0       | 191.0      | 35.0        |  |  |

| REF4132B30DBVRQ1           | SOT-23       | DBV             | 5    | 3000 | 213.0       | 191.0      | 35.0        |  |  |

| REF4132B33DBVRQ1           | SOT-23       | DBV             | 5    | 3000 | 213.0       | 191.0      | 35.0        |  |  |

| REF4132B40DBVRQ1           | SOT-23       | DBV             | 5    | 3000 | 213.0       | 191.0      | 35.0        |  |  |

| REF4132B50DBVRQ1           | SOT-23       | DBV             | 5    | 3000 | 213.0       | 191.0      | 35.0        |  |  |

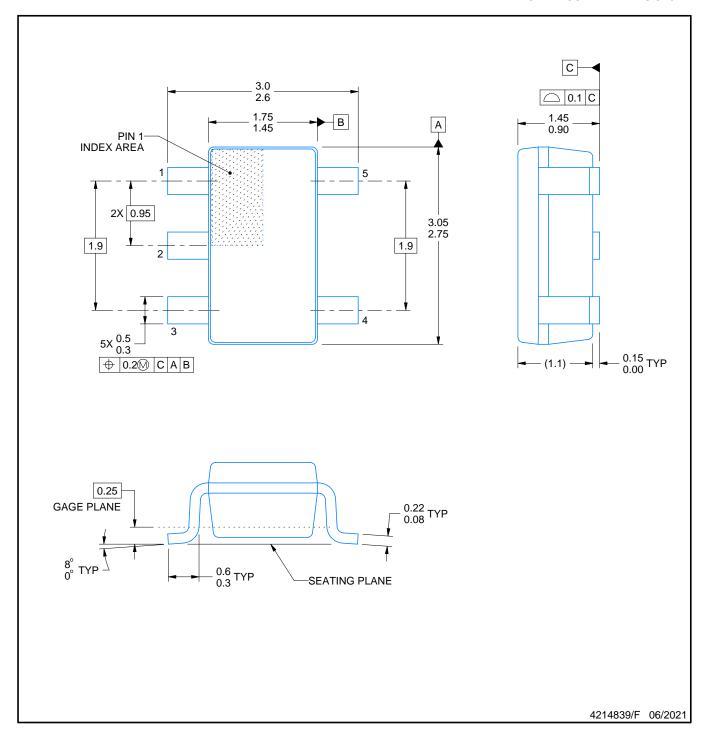

SMALL OUTLINE TRANSISTOR

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-178.

- 4. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

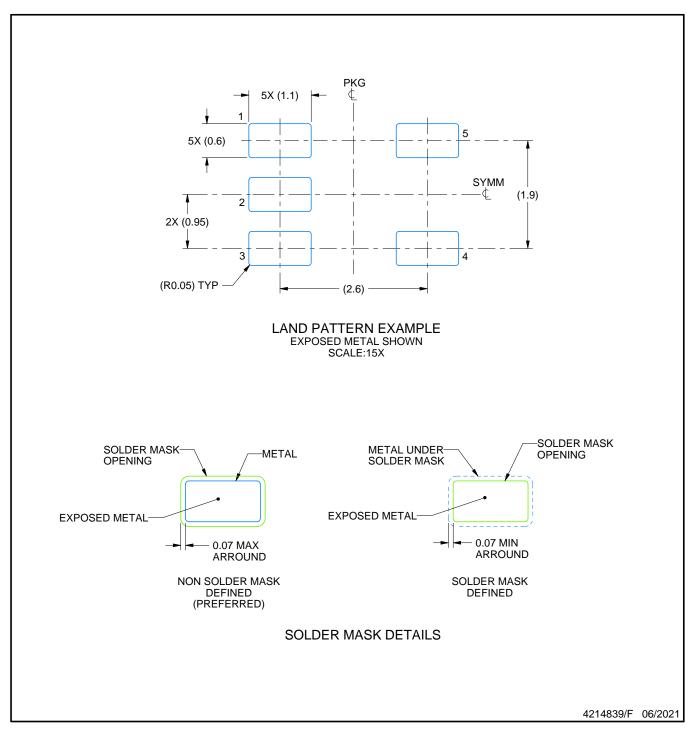

5. Publication IPC-7351 may have alternate designs.6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

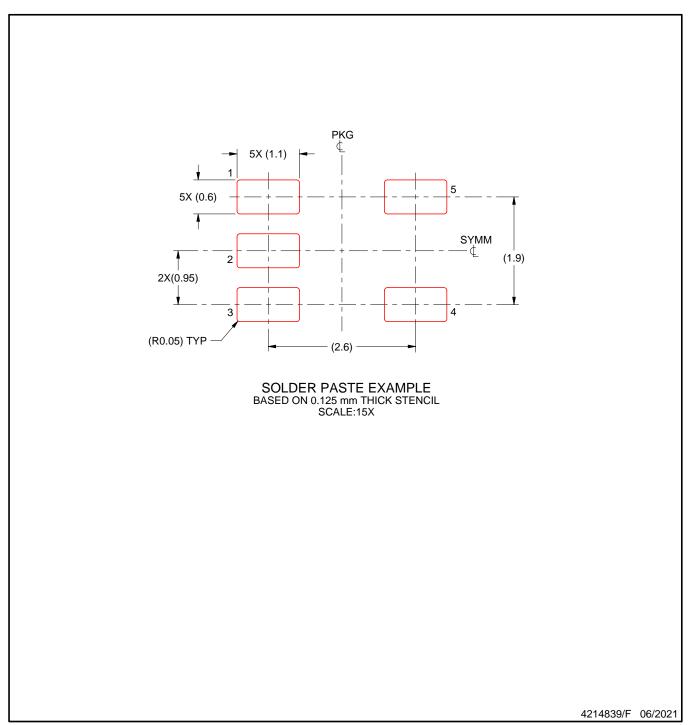

<sup>7.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

<sup>8.</sup> Board assembly site may have different recommendations for stencil design.