SLVSCK7E - DECEMBER 2014-REVISED MAY 2020

# TPS6217x-Q1 3-V to17-V 0.5-A Step-Down Converters with DCS-Control™

## Features

- DCS-Control<sup>™</sup> topology

- Qualified for automotive applications

- AEC-Q100 qualified with the following results:

- Device temperature grade: -40°C to 125°C operating junction temperature range

- Device HBM ESD classification level H2

- Device CDM ESD classification level C4B

- **Functional Safety-Capable**

- Documentation available to aid functional safety system design

- Input voltage range: 3 V to 17 V

- Up to 500-mA output current

- Adjustable output voltage from 0.9 V to 6 V

- Fixed output voltage versions

- Seamless power save mode transition

- Typically 17-µA quiescent current

- Power-good output

- 100% Duty cycle mode

- Short circuit protection

- Overtemperature protection

- Pin-to-pin compatible with TPS62160-Q1

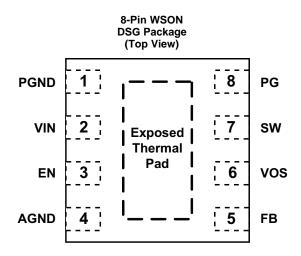

- Available in a 2 x 2 mm, WSON-8 package

- Create a custom design using the TPS62170-Q1 • with the WEBENCH<sup>®</sup> power designer

## 2 Applications

- ADAS camera

- **Powertrain systems**

- Body electronics and lighting

- Automotive infotainment and cluster

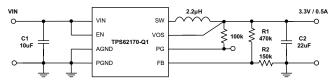

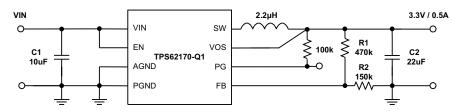

#### **Typical Application Schematic**

## 3 Description

The TPS6217x-Q1 family is an easy to use synchronous step-down DC-DC converter optimized for applications with high power density. A high switching frequency of typically 2.25 MHz allows the use of small inductors and provides fast transient response as well as high output voltage accuracy by utilization of the DCS-Control topology.

With their wide operating input voltage range of 3 V to 17 V, the devices are ideally suited for systems powered from either a Li-Ion or other battery as well as from 12-V intermediate power rails. It supports up to 0.5-A continuous output current at output voltages between 0.9 V and 6 V (with 100% duty cycle mode).

Power sequencing is also possible by configuring the Enable and open-drain Power Good pins.

In Power Save Mode, the devices draw guiescent current of about 17 µA from VIN. Power Save Mode, entered automatically and seamlessly if load is small, maintains high efficiency over the entire load range. In Shutdown Mode, the device is turned off and shutdown current consumption is less than 2 µA.

The device, available in adjustable and fixed output voltage versions, is packaged in an 8-pin WSON package measuring  $2 \times 2 \text{ mm}$  (DSG).

#### Device Information<sup>(1)</sup>

| PART NUMBER                                         | PACKAGE                          | BODY SIZE (NOM)   |  |  |

|-----------------------------------------------------|----------------------------------|-------------------|--|--|

| TPS62170-Q1                                         | WSON (8)                         | 2.00 mm × 2.00 mm |  |  |

| TPS62171-Q1                                         | TPS62171-Q1 WSON (8) 2.00 mm × 2 |                   |  |  |

| TPS62172-Q1         WSON (8)         2.00 mm × 2.00 |                                  | 2.00 mm × 2.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

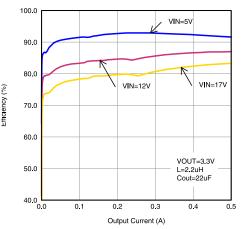

#### **Efficiency versus Output Current**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# **Table of Contents**

| 1 | Feat | tures 1                           |

|---|------|-----------------------------------|

| 2 | Арр  | lications1                        |

| 3 |      | cription1                         |

| 4 | Rev  | ision History 2                   |

| 5 |      | ice Comparison Table 4            |

| 6 | Pin  | Configuration and Functions 4     |

| 7 | Spe  | cifications5                      |

|   | 7.1  | Absolute Maximum Ratings 5        |

|   | 7.2  | ESD Ratings5                      |

|   | 7.3  | Recommended Operating Conditions5 |

|   | 7.4  | Thermal Information 5             |

|   | 7.5  | Electrical Characteristics        |

|   | 7.6  | Typical Characteristics 7         |

| 8 | Deta | ailed Description8                |

|   | 8.1  | Overview                          |

|   | 8.2  | Functional Block Diagram 8        |

|   | 8.3  | Feature Description               |

|   | 8.4  | Device Functional Modes9          |

| 9 | Арр  | lication and Implementation 12    |

|    | 9.1  | Application Information           | 12 |

|----|------|-----------------------------------|----|

|    | 9.2  | Typical TPS62170-Q1 Application   | 12 |

|    | 9.3  | System Examples                   | 20 |

| 10 | Pow  | ver Supply Recommendations        | 22 |

| 11 | Lay  | out                               | 23 |

|    | 11.1 | Layout Guidelines                 | 23 |

|    | 11.2 | Layout Example                    | 23 |

|    | 11.3 | Thermal Considerations            | 23 |

| 12 | Dev  | ice and Documentation Support     | 25 |

|    | 12.1 | Device Support                    | 25 |

|    | 12.2 | Documentation Support             | 25 |

|    | 12.3 | Related Links                     | 26 |

|    | 12.4 | Trademarks                        | 26 |

|    | 12.5 | Electrostatic Discharge Caution   | 26 |

|    | 12.6 |                                   |    |

|    | 12.7 | Support Resources                 | 26 |

|    | 12.8 | Glossary                          | 26 |

| 13 | Mec  | hanical, Packaging, and Orderable |    |

|    | Info | rmation                           | 26 |

|    |      |                                   |    |

Page

Page

## **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision D (February 2017) to Revision E                                                              | Page |

|--------------------------------------------------------------------------------------------------------------------|------|

| Added functional safety bullet in the <i>Features</i>                                                              | 1    |

| Changes from Revision C (November 2016) to Revision D                                                              | Page |

| Added WEBENCH <sup>®</sup> information                                                                             | 1    |

| <ul> <li>Changed T<sub>J</sub> spec MAX value From 125°C To 150°C in the Absolute Maximum Ratings table</li> </ul> | 5    |

| Changes from Revision B (October 2016) to Revision C                                                               | Page |

| Added Pin to Pin compatible feature                                                                                | 1    |

| Changed Thermal Information table                                                                                  | 5    |

| Added C1, C2, R1, R2, descriptors to Figure 5.                                                                     | 12   |

| Added C1, C2 to Table 1                                                                                            | 12   |

#### Changes from Revision A (September 2016) to Revision B

| • | Added the Device Comparison Table | 4 |

|---|-----------------------------------|---|

## Changes from Original (December 2014) to Revision A

| • | Changed "POE Over Coax POL Supply " To: "Power Over Coax POL Supply " in the Application list 1                         |

|---|-------------------------------------------------------------------------------------------------------------------------|

| • | Added TPS62171-Q1 device to data sheet                                                                                  |

| • | Changed Unit from mA to V for Pin voltage at FB, PG, and VOS in the Absolute Maximum Ratings table                      |

| • | Changed Unit from °C to mA in the Absolute Maximum Ratings table for Power Good sink current                            |

| • | Changed Unit from kV to °C in the Absolute Maximum Ratings table for the Operating junction temperature, T <sub>J</sub> |

# TPS62170-Q1, TPS62171-Q1, TPS62172-Q1

SLVSCK7E - DECEMBER 2014-REVISED MAY 2020

| • | Added legal NOTE at Application and Implementation                   | 12 |

|---|----------------------------------------------------------------------|----|

| • | Added cross references to Third-Party Products disclaimer in Table 1 | 12 |

# 5 Device Comparison Table

| PART NUMBER <sup>(1)</sup> | OUTPUT VOLTAGE |

|----------------------------|----------------|

| TPS62170-Q1                | Adjustable     |

| TPS62171-Q1                | 1.8 V          |

| TPS62172-Q1                | 3.3 V          |

<sup>(1)</sup> For detailed ordering information, please check the *Mechanical, Packaging, and Orderable Information* section at the end of this data sheet.

## 6 Pin Configuration and Functions

### **Pin Functions**

| PIN <sup>(1)</sup> NAME NUMBER |   | 1/0                                                                                                                                                                   | DESCRIPTION                                                                                                                                                                                       |  |

|--------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                |   | 1/0                                                                                                                                                                   | DESCRIPTION                                                                                                                                                                                       |  |

| PGND                           | 1 |                                                                                                                                                                       | Power ground                                                                                                                                                                                      |  |

| VIN                            | 2 | Ι                                                                                                                                                                     | Supply voltage                                                                                                                                                                                    |  |

| EN                             | 3 | I                                                                                                                                                                     | Enable input (High = enabled, Low = disabled)                                                                                                                                                     |  |

| AGND                           | 4 |                                                                                                                                                                       | Analog ground                                                                                                                                                                                     |  |

| FB                             | 5 | I                                                                                                                                                                     | Voltage feedback of adjustable version. Connect resistive voltage divider to this pin. It is recommended to connect FB to AGND on fixed output voltage versions for improved thermal performance. |  |

| VOS                            | 6 | I                                                                                                                                                                     | Output voltage sense pin and connection for the control loop circuitry                                                                                                                            |  |

| SW 7 (                         |   | 0                                                                                                                                                                     | Switch node, which is connected to the internal MOSFET switches. Connect inductor between SW and output capacitor.                                                                                |  |

| PG                             | 8 | O Output power good (High = VOUT ready, Low = VOUT below nominal regulation); open drain (required pullup resistor; goes high impedance, when device is switched off) |                                                                                                                                                                                                   |  |

| Exposed<br>Thermal Pad         |   |                                                                                                                                                                       | Must be connected to AGND. Must be soldered to achieve appropriate power dissipation and mechanical reliability.                                                                                  |  |

(1) For more information about connecting pins, see the Detailed Description and Application and Implementation sections.

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating junction temperature range (unless otherwise noted) <sup>(1)</sup>

|                                             |             | MIN  | MAX                  | UNIT |

|---------------------------------------------|-------------|------|----------------------|------|

|                                             | VIN         | -0.3 | 20                   | V    |

| Pin voltage <sup>(2)</sup>                  | EN          | -0.3 | V <sub>IN</sub> +0.3 | V    |

| n voitage/                                  | SW          | -0.3 | V <sub>IN</sub> +0.3 | V    |

|                                             | FB, PG, VOS | -0.3 | 7                    | V    |

| Power Good sink current                     | PG          |      | 10                   | mA   |

| Operating junction temperature range, $T_J$ |             | -40  | 150                  | °C   |

| Storage temperature range, T <sub>stg</sub> |             | -65  | 150                  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to network ground terminal.

## 7.2 ESD Ratings

|                                            |                                              |                                                         | VALUE | UNIT |

|--------------------------------------------|----------------------------------------------|---------------------------------------------------------|-------|------|

| M                                          |                                              | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged device model (CDM), per AEC Q100-011 | ±500                                                    | V     |      |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 7.3 Recommended Operating Conditions

over operating junction temperature range (unless otherwise noted)

|                  |                                | MIN | TYP | MAX | UNIT |

|------------------|--------------------------------|-----|-----|-----|------|

| V <sub>IN</sub>  | Supply voltage                 | 3   |     | 17  | V    |

| V <sub>OUT</sub> | Output voltage range           | 0.9 |     | 6   | V    |

| TJ               | Operating junction temperature | -40 |     | 125 | °C   |

## 7.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | TPS6217x-Q1  |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       |                                              | DSG (8 PINS) | UNIT |

| $R_{	hetaJA}$         | Junction-to-ambient thermal resistance       | 65.5         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 66.4         | °C/W |

| $R_{\thetaJB}$        | Junction-to-board thermal resistance         | 35.5         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 1.7          | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 35.8         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 8.4          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

SLVSCK7E – DECEMBER 2014 – REVISED MAY 2020

## 7.5 Electrical Characteristics

over junction temperature range ( $T_1 = -40^{\circ}$ C to +125°C), typical values at  $V_{IN} = 12$  V and  $T_1 = 25^{\circ}$ C (unless otherwise noted)

|                     | PARAMETER                                             | TEST CONDITIONS                                                                                                                                                | MIN   | TYP  | MAX  | UNIT  |

|---------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|

| SUPPL               | (                                                     |                                                                                                                                                                |       |      |      |       |

| V <sub>IN</sub>     | Input voltage range <sup>(1)</sup>                    |                                                                                                                                                                | 3     |      | 17   | V     |

| lq                  | Operating quiescent current                           | EN = High, IOUT = 0 mA, Device not switching                                                                                                                   |       | 17   | 30   | μA    |

| I <sub>SD</sub>     | Shutdown current <sup>(2)</sup>                       | EN = Low                                                                                                                                                       |       | 1.8  | 25   | μA    |

|                     |                                                       | Falling input voltage                                                                                                                                          | 2.6   | 2.7  | 2.82 | V     |

| V <sub>UVLO</sub>   | Undervoltage lockout threshold                        | Hysteresis                                                                                                                                                     |       | 180  |      | mV    |

| <b>-</b>            | Thermal shutdown temperature                          |                                                                                                                                                                |       | 160  |      |       |

| T <sub>SD</sub>     | Thermal shutdown hysteresis                           |                                                                                                                                                                |       | 20   |      | °C    |

| CONTR               | OL (EN, PG)                                           |                                                                                                                                                                |       |      |      |       |

| V <sub>EN_H</sub>   | High-level input threshold voltage (EN)               |                                                                                                                                                                | 0.9   |      |      | V     |

| V <sub>EN_L</sub>   | Low-level input threshold voltage (EN)                |                                                                                                                                                                |       |      | 0.3  | V     |

| I <sub>LKG_EN</sub> | Input leakage current (EN)                            | EN = V <sub>IN</sub> or GND                                                                                                                                    |       | 0.01 | 1    | μA    |

|                     | Devues Cool threads ald walte as                      | Rising (%V <sub>OUT</sub> )                                                                                                                                    | 92%   | 95%  | 98%  |       |

| V <sub>TH_PG</sub>  | Power Good threshold voltage                          | Falling (%V <sub>OUT</sub> )                                                                                                                                   | 87%   | 90%  | 93%  |       |

| V <sub>OL_PG</sub>  | Power Good output low                                 | $I_{PG} = -2 \text{ mA}$                                                                                                                                       |       | 0.07 | 0.3  | V     |

| I <sub>LKG_PG</sub> | Input leakage current (PG)                            | V <sub>PG</sub> = 1.8 V                                                                                                                                        |       | 1    | 400  | nA    |

| POWER               | SWITCH                                                |                                                                                                                                                                |       |      |      |       |

|                     | Lligh side MOSEET ON resistance                       | V <sub>IN</sub> ≥ 6 V                                                                                                                                          |       | 300  | 600  |       |

| Р                   | High-side MOSFET ON-resistance                        | V <sub>IN</sub> = 3 V                                                                                                                                          |       | 430  |      | mΩ    |

| R <sub>DS(ON)</sub> | Low-side MOSFET ON-resistance                         | V <sub>IN</sub> ≥ 6 V                                                                                                                                          |       | 120  | 200  |       |

|                     | Low-side MOSFET ON-resistance                         | V <sub>IN</sub> = 3 V                                                                                                                                          |       | 165  |      | mΩ    |

| I <sub>LIMF</sub>   | High-side MOSFET forward current limit <sup>(3)</sup> | $V_{IN} = 12 \text{ V}, \text{ T}_{A} = 25^{\circ}\text{C}$                                                                                                    | 0.85  | 1.05 | 1.35 | А     |

| OUTPU               | г                                                     |                                                                                                                                                                |       |      |      |       |

| VREF                | Internal reference voltage                            |                                                                                                                                                                |       | 0.8  |      | V     |

| I <sub>LKG_FB</sub> | Pin leakage current (FB)                              | TPS62170-Q1, V <sub>FB</sub> = 1.2 V                                                                                                                           |       | 5    | 400  | nA    |

|                     | Output voltage range                                  | TPS62170-Q1, V <sub>IN</sub> ≥ V <sub>OUT</sub>                                                                                                                | 0.9   |      | 6.0  | V     |

|                     | Feedback voltage accuracy <sup>(4)</sup>              | PWM Mode operation, $V_{IN} \ge V_{OUT} + 1 V$                                                                                                                 | -3%   |      | 3%   |       |

| V <sub>OUT</sub>    |                                                       | Power Save Mode operation, $C_{OUT}$ = 22 $\mu F^{(5)}$                                                                                                        | -3.5% |      | 4%   |       |

| • 001               | DC output voltage load regulation <sup>(6)</sup>      | $V_{IN}$ = 12 V, $V_{OUT}$ = 3.3 V, PWM Mode operation                                                                                                         |       | 0.05 |      | % / A |

|                     | DC output voltage line regulation <sup>(6)</sup>      | $3 \text{ V} \le \text{V}_{\text{IN}} \le 17 \text{ V}, \text{ V}_{\text{OUT}} = 3.3 \text{ V}, \text{ I}_{\text{OUT}} = 0.5 \text{ A},$<br>PWM Mode operation |       | 0.02 |      | % / V |

(1) The device is still functional down to Under Voltage Lockout (see parameter V<sub>UVLO</sub>).

Current into VIN pin (2)

(3) This is the static current limit. It can be temporarily higher in applications due to internal propagation delay (see Current Limit and Short Circuit Protection).

For fixed voltage versions, the (internal) resistive feedback divider is included. (4)

The accuracy in Power Save Mode can be improved by increasing the  $C_{OUT}$  value, reducing the output voltage ripple. Line and load regulation are depending on external component selection and layout (see Figure 14 and Figure 15). (5)

(6)

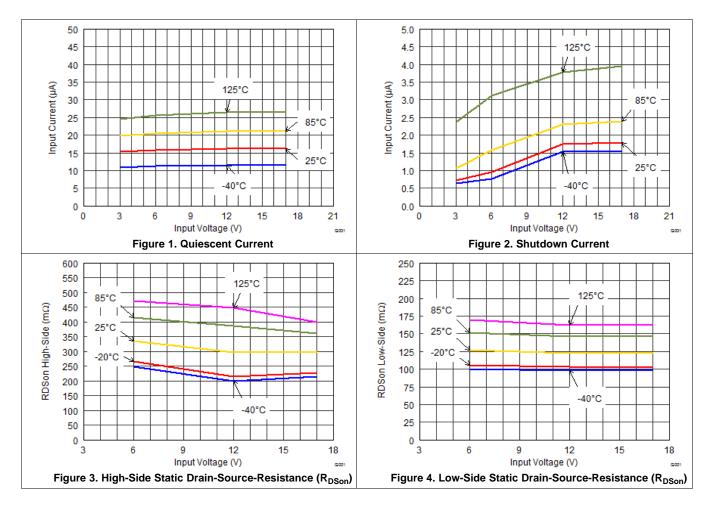

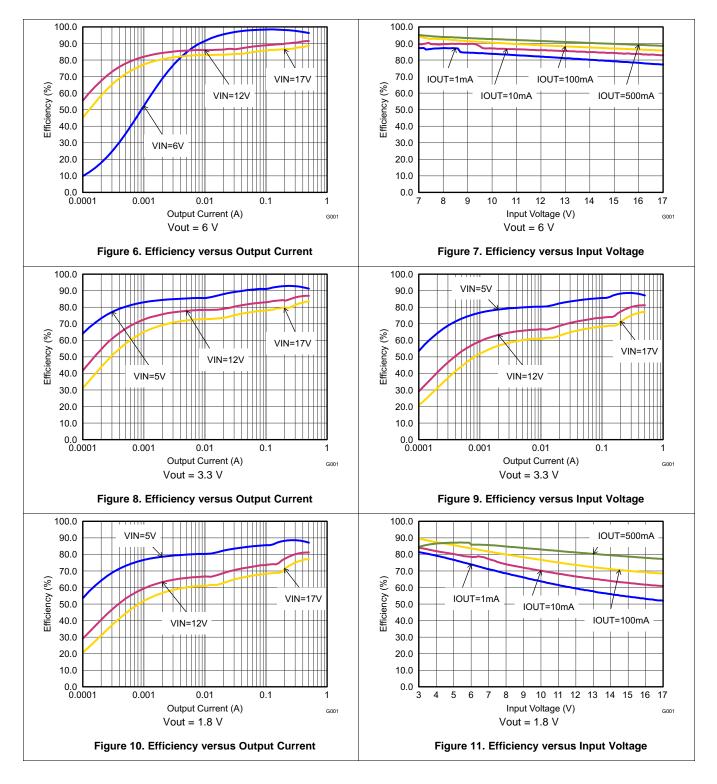

# 7.6 Typical Characteristics

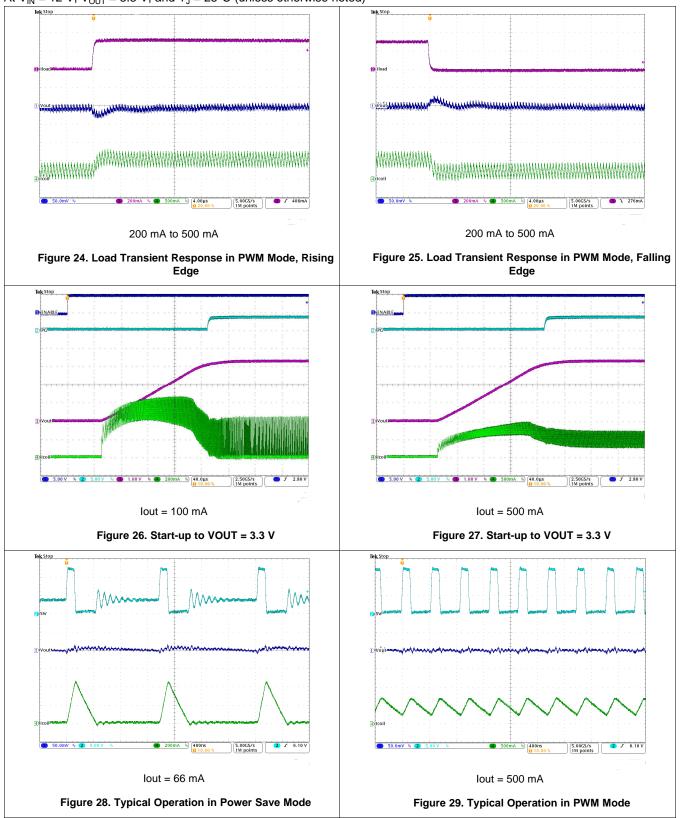

At V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 3.3 V and T<sub>J</sub> = 25°C (unless otherwise noted)

# 8 Detailed Description

## 8.1 Overview

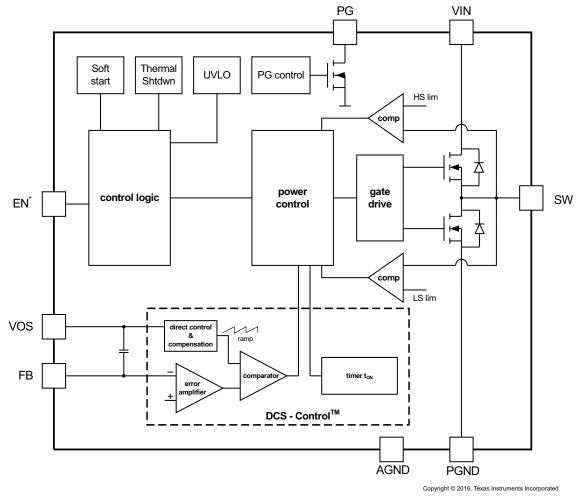

The TPS6217x-Q1 synchronous switched mode power converters are based on DCS-Control (**D**irect **C**ontrol with **S**eamless transition into power save mode), an advanced regulation topology, that combines the advantages of hysteretic, voltage mode, and current mode control including an AC loop directly associated to the output voltage. This control loop takes information about output voltage changes and feeds it directly to a fast comparator stage. It sets the switching frequency, which is constant for steady state operating conditions, and provides immediate response to dynamic load changes. To get accurate DC load regulation, a voltage feedback loop is used. The internally compensated regulation network achieves fast and stable operation with small external components and low ESR capacitors.

The DCS-Control<sup>™</sup> topology supports PWM (Pulse Width Modulation) mode for medium and heavy load conditions and a Power Save Mode at light loads. During PWM, it operates at its nominal switching frequency in continuous conduction mode. This frequency is typically about 2.25 MHz with a controlled frequency variation depending on the input voltage. If the load current decreases, the converter enters Power Save Mode to sustain high efficiency down to very light loads. In Power Save Mode, the switching frequency decreases linearly with the load current. Since DCS-Control supports both operation modes within one single building block, the transition from PWM to Power Save Mode is seamless without affecting the output voltage.

## 8.2 Functional Block Diagram

\*This pin is connected to a pull down resistor internally (see the Feature Description section).

## 8.3 Feature Description

## 8.3.1 Enable / Shutdown (EN)

When Enable (EN) is set High, the device starts operation.

Shutdown is forced if EN is pulled Low with a shutdown current of typically 1.8  $\mu$ A. During shutdown, the internal power MOSFETs as well as the entire control circuitry are turned off. The internal resistive divider pulls down the output voltage smoothly. If the EN pin goes Low, an internal pulldown resistor of about 400 k $\Omega$  is connected and keeps it Low in case of floating pin. To avoid ON/OFF oscillations, a minimum slew rate of about 50 mV/s is recommended for the EN signal.

Connecting the EN pin to an appropriate output signal of another power rail provides sequencing of multiple power rails.

## 8.3.2 Soft Start

The internal soft start circuitry controls the output voltage slope during start-up. This avoids excessive inrush current and ensures a controlled output voltage rise time. It also prevents unwanted voltage drops from high-impedance power sources or batteries. When EN is set to start device operation, the device starts switching after a delay of about 50  $\mu$ s and V<sub>OUT</sub> rises with a slope of about 25 mV/ $\mu$ s. See Figure 26 and Figure 27 for typical start-up operation.

The TPS6217x-Q1 can start into a pre-biased output. During monotonic pre-biased start-up, the low-side MOSFET is not allowed to turn on until the internal ramp of the device sets an output voltage above the pre-bias voltage.

#### 8.3.3 Power Good (PG)

The TPS6217x-Q1 has a built-in power good (PG) function to indicate whether the output voltage has reached its appropriate level or not. The PG signal can be used for start-up sequencing of multiple rails. The PG pin is an open-drain output that requires a pullup resistor (to any voltage below 7 V). It can sink 2 mA of current and maintain its specified logic low level. It is high impedance when the device is turned off due to EN, UVLO, or thermal shutdown.

#### 8.3.4 Undervoltage Lockout (UVLO)

If the input voltage drops, the undervoltage lockout prevents misoperation of the device by switching off both the power FETs. The undervoltage lockout threshold is set typically to 2.7 V. The device is fully operational for voltages above the UVLO threshold and turns off if the input voltage trips the threshold. The converter starts operation again once the input voltage exceeds the threshold by a hysteresis of typically 180 mV.

#### 8.3.5 Thermal Shutdown

The junction temperature  $(T_J)$  of the device is monitored by an internal temperature sensor. If  $T_J$  exceeds 160°C (typ), the device goes into thermal shut down. Both the high-side and low-side power FETs are turned off and PG goes high impedance. When  $T_J$  decreases below the hysteresis amount, the converter resumes normal operation, beginning with soft start. To avoid unstable conditions, a hysteresis of typically 20°C is implemented on the thermal shut down temperature.

## 8.4 Device Functional Modes

#### 8.4.1 Pulse Width Modulation (PWM) Operation

The TPS62170-Q1 operates with pulse width modulation in continuous conduction mode (CCM) with a nominal switching frequency of about 2.25 MHz. The frequency variation in PWM is controlled and depends on  $V_{IN}$ ,  $V_{OUT}$ , and the inductance. The device operates in PWM mode as long the output current is higher than half the ripple current of the inductor. To maintain high efficiency at light loads, the device enters Power Save Mode at the boundary to discontinuous conduction mode (DCM). This happens if the output current becomes smaller than half the ripple current of the inductor.

#### **Device Functional Modes (continued)**

#### 8.4.2 Power Save Mode Operation

The built-in Power Save Mode of the TPS6217x-Q1 is entered seamlessly, if the load current decreases. This secures a high efficiency in light load operation. The device remains in Power Save Mode as long as the inductor current is discontinuous.

In Power Save Mode, the switching frequency decreases linearly with the load current maintaining high efficiency. The transition in and out of Power Save Mode happens within the entire regulation scheme and is seamless in both directions.

The TPS6217x-Q1 includes a fixed on-time circuitry. This on-time, in steady-state operation, can be estimated as:

$$t_{ON} = \frac{V_{OUT}}{V_{IN}} \cdot 420ns \tag{1}$$

For very small output voltages, the on-time increases beyond the result of Equation 1 to stay above an absolute minimum on-time,  $t_{ON(min)}$ , which is around 80 ns to limit switching losses. The peak inductor current in PSM can be approximated by:

$$I_{LPSM(peak)} = \frac{(V_{IN} - V_{OUT})}{L} \cdot t_{ON}$$

<sup>(2)</sup>

When  $V_{IN}$  decreases to typically 15% above  $V_{OUT}$ , the TPS62170-Q1 does not enter Power Save Mode, regardless of the load current. The device maintains output regulation in PWM mode.

#### 8.4.3 100% Duty-Cycle Operation

The duty cycle of the buck converter is given by D = Vout / Vin and increases as the input voltage comes close to the output voltage. In this case, the device starts 100% duty cycle operation turning on the high-side switch 100% of the time. The high-side switch stays turned on as long as the output voltage is below the internal setpoint. This allows the conversion of small input to output voltage differences (for example, for longest operation time of battery-powered applications). In 100% duty cycle mode, the low-side FET is switched off.

The minimum input voltage to maintain output voltage regulation, depending on the load current and the output voltage level, can be calculated as:

$$V_{IN(min)} = V_{OUT(min)} + I_{OUT} \left( R_{DS(on)} + R_L \right)$$

where

- I<sub>OUT</sub> is the output current

- R<sub>DS(on)</sub> is the R<sub>DS(on)</sub> of the high-side FET

- R<sub>L</sub> is the DC resistance of the inductor used

(3)

#### 8.4.4 Current Limit and Short Circuit Protection

The TPS6217x-Q1 devices are protected against heavy load and short circuit events. At heavy loads, the current limit determines the maximum output current. If the current limit is reached, the high-side FET is turned off. Avoiding shoot through current, the low-side FET is then switched on to allow the inductor current to decrease. The high-side FET turns on again, only if the current in the low-side FET has decreased below the low side current limit threshold.

The output current of the device is limited by the current limit (see the *Electrical Characteristics*). Due to internal propagation delay, the actual current can exceed the static current limit during that time. The dynamic current limit can be calculated as follows:

$$I_{peak(typ)} = I_{LIMF} + \frac{V_L}{L} \cdot t_{PD}$$

where

- ILIMF is the static current limit, specified in the electrical characteristic table

- L is the inductor value

- V<sub>L</sub> is the voltage across the inductor

- t<sub>PD</sub> is the internal propagation delay

(5)

### **Device Functional Modes (continued)**

The dynamic high side switch peak current can be calculated as follows:

$$I_{peak(typ)} = I_{LIMF_{HS}} + \frac{(V_{IN} - V_{OUT})}{L} \cdot 30ns$$

Care on the current limit has to be taken if the input voltage is high and very small inductances are used.

#### 8.4.5 Operation Above T<sub>J</sub> = 125°C

The operating junction temperature of the device is specified up to 125°C. In power supply circuits, the self heating effect causes the junction temperature,  $T_J$ , to be even higher than the ambient temperature  $T_A$ . Depending on  $T_A$  and the load current, the maximum operating temperature  $T_J$  can be exceeded. However, the electrical characteristics are specified up to a  $T_J$  of 125°C only. The device operates as long as thermal shutdown threshold is not triggered.

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1 Application Information

The following information is intended to be a guideline through the individual power supply design process.

## 9.2 Typical TPS62170-Q1 Application

Figure 5. 3.3-V/0.5-A Power Supply

#### 9.2.1 Design Requirements

The step-down converter design can be adapted to different output voltage and load current needs by choosing external components appropriate. The following design procedure is adequate for whole VIN, VOUT, and load current range of the TPS62170-Q1. Using Table 2, the design procedure needs minimum effort.

| REFERENCE | DESCRIPTION                           | MANUFACTURER <sup>(1)</sup>     |

|-----------|---------------------------------------|---------------------------------|

| IC        | 17-V, 0.5-A step-down converter, WSON | TPS62170QDSG, Texas Instruments |

| L1        | 2.2-μH, 1.4-A, 3 x 2.8 x 1.2 mm       | VLF3012ST-2R2M1R4, TDK          |

| C1        | 10-µF, 25-V, ceramic                  | Standard                        |

| C2        | 22-µF, 6.3-V, ceramic                 | Standard                        |

| R1        | Depending on Vout                     |                                 |

| R2        | Depending on Vout                     |                                 |

| R3        | 100-kΩ, chip, 0603, 1/16-W, 1%        | Standard                        |

(1) See *Third-Party Products* disclaimer.

## 9.2.2 Detailed Design Procedure

## 9.2.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the TPS62170-Q1 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 9.2.2.2 Programming the Output Voltage

While the output voltage of the TPS62170-Q1 is adjustable, the TPS62171-Q1 and TPS62172-Q1 are programmed to a fixed output voltage. For fixed output versions, the FB pin is pulled down internally and can be left floating. It is recommended to connect it to AGND to improve thermal resistance. The adjustable version can be programmed for output voltages from 0.9 V to 6 V by using a resistive divider from VOUT to FB to AGND. The voltage at the FB pin is regulated to 800 mV. The value of the output voltage is set by the selection of the resistive divider from Equation 6. It is recommended to choose resistor values which allow a cross current of at least 2 µA, meaning the value of R2 must not exceed 400 kΩ. Lower resistor values are recommended for the highest accuracy and most robust design. For applications requiring lowest current consumption, the use of fixed output voltage versions is recommended.

$$\mathsf{R}_1 = \mathsf{R}_2 \bigg( \frac{\mathsf{V}_{\text{OUT}}}{0.8\mathsf{V}} - 1 \bigg) \tag{6}$$

In case the FB pin gets opened, the device clamps the output voltage at the VOS pin to about 7.4 V.

#### 9.2.2.3 External Component Selection

The external components have to fulfill the needs of the application, but also the stability criteria of the devices control loop. The TPS62170-Q1 is optimized to work within a range of external components. The LC output filters inductance and capacitance have to be considered together, creating a double pole, responsible for the corner frequency of the converter (see the Output Filter and Loop Stability section). Table 2 can be used to simplify the output filter component selection.

|        | 4.7 µF | 10 µF        | 22 µF            | 47 µF        | 100 µF       | 200 µF       | 400 µF |

|--------|--------|--------------|------------------|--------------|--------------|--------------|--------|

| 1 µH   |        |              |                  |              |              |              |        |

| 2.2 µH |        | $\checkmark$ | √ <sup>(2)</sup> | $\checkmark$ | $\checkmark$ | $\checkmark$ |        |

| 3.3 µH |        | $\checkmark$ | $\checkmark$     | $\checkmark$ | $\checkmark$ |              |        |

| 4.7 µH |        |              |                  |              |              |              |        |

Table 2. Recommended LC Output Filter Combinations<sup>(1)</sup>

(1) The values in the table are nominal values. Variations of typically ±20% due to tolerance, saturation, and DC bias are assumed.

(2) This LC combination is the standard value and recommended for most applications.

More detailed information on further LC combinations can be found in the Optimizing the TPS62130/40/50/60 Output Filter Application Report.

#### 9.2.2.3.1 Inductor Selection

The inductor selection is affected by several effects like inductor ripple current, output ripple voltage, PWM-to-PSM transition point, and efficiency. In addition, the inductor selected has to be rated for appropriate saturation current and DC resistance (DCR). Equation 7 and Equation 8 calculate the maximum inductor current under static load conditions.

$$\begin{split} I_{L(\max)} &= I_{OUT(\max)} + \frac{\Delta I_{L(\max)}}{2} \\ \Delta I_{L(\max)} &= V_{OUT} \cdot \left( \frac{1 - \frac{V_{OUT}}{V_{IN(\max)}}}{L_{(\min)} \cdot f_{SW}} \right) \end{split}$$

where

- $I_{I}$  (max) is the maximum inductor current

- $\Delta I_{I}$  is the peak-to-peak inductor ripple current

- L(min) is the minimum effective inductor value

- f<sub>SW</sub> is the actual PWM switching frequency

(7)

#### TPS62170-Q1, TPS62171-Q1, TPS62172-Q1

#### SLVSCK7E - DECEMBER 2014 - REVISED MAY 2020

Calculating the maximum inductor current using the actual operating conditions gives the minimum saturation current of the inductor needed. A margin of about 20% is recommended to add. A larger inductor value is also useful to get lower ripple current, but increases the transient response time and size as well. The following inductors have been used with the TPS62170-Q1 and are recommended for use:

| TYPE              | INDUCTANCE [µH] | CURRENT [A] <sup>(1)</sup> | DIMENSIONS [L x B x H] mm | MANUFACTURER <sup>(2)</sup> |

|-------------------|-----------------|----------------------------|---------------------------|-----------------------------|

| VLF3012ST-2R2M1R4 | 2.2 μH, ±20%    | 1.9 A                      | 3.0 x 2.8 x 1.2           | TDK                         |

| VLF302512MT-2R2M  | 2.2 μH, ±20%    | 1.9 A                      | 3.0 x 2.5 x 1.2           | TDK                         |

| VLS252012-2R2     | 2.2 μH, ±20%    | 1.3 A                      | 2.5 x 2.0 x 1.2           | TDK                         |

| XFL3012-222MEC    | 2.2 μH, ±20%    | 1.9 A                      | 3.0 x 3.0 x 1.2           | Coilcraft                   |

| XFL3012-332MEC    | 3.3 μH, ±20%    | 1.6 A                      | 3.0 x 3.0 x 1.2           | Coilcraft                   |

| XPL2010-222MLC    | 2.2 μH, ±20%    | 1.3 A                      | 1.9 x 2.0 x 1.0           | Coilcraft                   |

| XPL2010-332MLC    | 3.3 μH, ±20%    | 1.1 A                      | 1.9 x 2.0 x 1.0           | Coilcraft                   |

| LPS3015-332ML     | 3.3 μH, ±20%    | 1.4 A                      | 3.0 x 3.0 x 1.4           | Coilcraft                   |

| PFL2512-222ME     | 2.2 μH, ±20%    | 1.0 A                      | 2.8 x 2.3 x 1.2           | Coilcraft                   |

| PFL2512-333ME     | 3.3 μH, ±20%    | 0.78 A                     | 2.8 x 2.3 x 1.2           | Coilcraft                   |

| 744028003         | 3.3 μH, ±30%    | 1.0 A                      | 2.8 x 2.8 x 1.1           | Wuerth                      |

| PSI25201B-2R2MS   | 2.2 μH, ±20%    | 1.3 A                      | 2.0 x 2.5 x 1.2           | Cyntec                      |

| NR3015T-2R2M      | 2.2 μH, ±20%    | 1.5 A                      | 3.0 x 3.0 x 1.5           | Taiyo Yuden                 |

| BRC2012T2R2MD     | 2.2 μH, ±20%    | 1.0 A                      | 2.0 x 1.25 x 1.4          | Taiyo Yuden                 |

| BRC2012T3R3MD     | 3.3 µH, ±20%    | 0.87 A                     | 2.0 x 1.25 x 1.4          | Taiyo Yuden                 |

| Table 3. List of Inductors | S |

|----------------------------|---|

|----------------------------|---|

I<sub>RMS</sub> at 40°C rise or I<sub>SAT</sub> at 30% drop.

See *Third-Party Products* disclaimer.

The TPS6217x-Q1 can be run with an inductor as low as 2.2  $\mu$ H. However, for applications running with low input voltages, 3.3  $\mu$ H is recommended to allow the full output current. The inductor value also determines the load current at which Power Save Mode is entered:

(9)

$$I_{load(PSM)} = \frac{1}{2} \Delta I_L$$

Using Equation 8, this current level can be adjusted by changing the inductor value.

#### 9.2.2.3.2 Capacitor Selection

#### 9.2.2.3.2.1 Output Capacitor

The recommended value for the output capacitor is 22 µF. The architecture of the TPS6217x-Q1 allows the use of tiny ceramic output capacitors with low equivalent series resistance (ESR). These capacitors provide low output voltage ripple and are recommended. To keep its low resistance up to high frequencies and to get narrow capacitance variation with temperature, it's recommended to use X7R or X5R dielectric. Using a higher value can have some advantages like smaller voltage ripple and a tighter DC output accuracy in Power Save Mode (see the *Optimizing the TPS62130/40/50/60 Output Filter Application Report*).

#### NOTE

In Power Save Mode, the output voltage ripple depends on the output capacitance, its ESR and the peak inductor current. Using ceramic capacitors provides small ESR and low ripple.

#### 9.2.2.3.2.2 Input Capacitor

For most applications, 10  $\mu$ F is sufficient and is recommended, though a larger value reduces input current ripple further. The input capacitor buffers the input voltage for transient events and also decouples the converter from the supply. A low ESR multilayer ceramic capacitor is recommended for best filtering and should be placed between VIN and GND as close as possible to those pins.

#### NOTE

**DC Bias effect:** High capacitance ceramic capacitors have a DC Bias effect, which will have a strong influence on the final effective capacitance. Therefore, the right capacitor value has to be chosen carefully. Package size and voltage rating in combination with dielectric material are responsible for differences between the rated capacitor value and the effective capacitance.

#### 9.2.2.4 Output Filter and Loop Stability

1

The devices of the TPS6217x-Q1 family are internally compensated to be stable with L-C filter combinations corresponding to a corner frequency to be calculated with Equation 10:

$$f_{LC} = \frac{1}{2\pi\sqrt{L \cdot C}} \tag{10}$$

Proven nominal values for inductance and ceramic capacitance are given in Table 2 and are recommended for use. Different values can work, but care has to be taken on the loop stability which might be affected. More information including a detailed L-C stability matrix can be found in the *Optimizing the TPS62130/40/50/60 Output Filter Application Report*.

The TPS6217x-Q1 devices, both fixed and adjustable versions, include an internal 25-pF feedforward capacitor, connected between the VOS and FB pins. This capacitor impacts the frequency behavior and sets a pole and zero in the control loop with the resistors of the feedback divider, per Equation 11 and Equation 12:

$$f_{zero} = \frac{1}{2\pi \cdot R_1 \cdot 25 pF}$$

$$f_{pole} = \frac{1}{2\pi \cdot 25 pF} \cdot \left(\frac{1}{R_1} + \frac{1}{R_2}\right)$$

$$(11)$$

Though the TPS6217x-Q1 devices are stable without the pole and zero being in a particular location, adjusting their location to the specific needs of the application can provide better performance in Power Save mode and improved transient response. An external feedforward capacitor can also be added. A more detailed discussion on the optimization for stability versus transient response can be found in the *Optimizing Transient Response of Internally Compensated DC-DC Converters Application Report* and *Feedforward Capacitor to Improve Stability and Bandwidth of TPS621/821-Family Application Report*.

If using ceramic capacitors, the DC bias effect has to be considered. The DC bias effect results in a drop in effective capacitance as the voltage across the capacitor increases (see the *DC Bias effect note* in the *Input Capacitor* section).

#### TPS62170-Q1, TPS62171-Q1, TPS62172-Q1

SLVSCK7E - DECEMBER 2014-REVISED MAY 2020

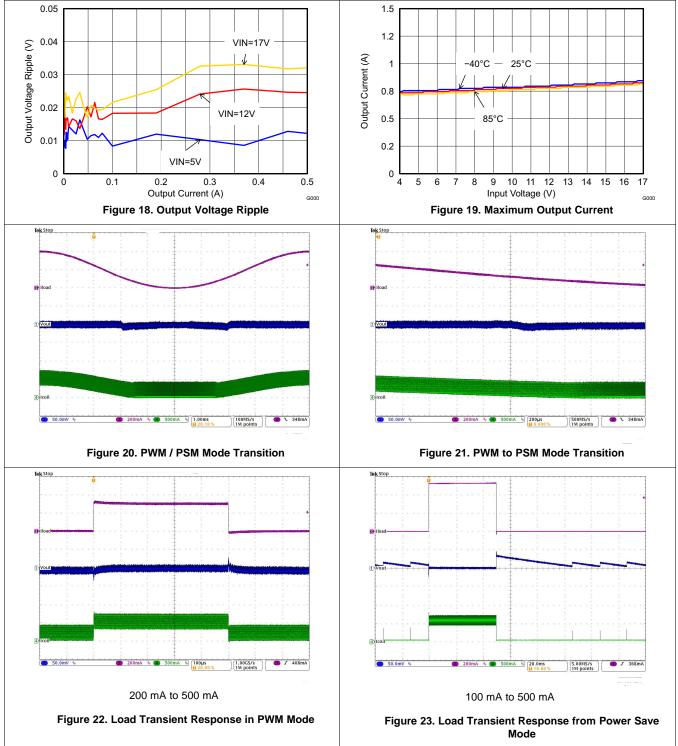

#### 9.2.3 Application Curves

At  $V_{IN}$  = 12 V,  $V_{OUT}$  = 3.3 V, and  $T_J$  = 25°C (unless otherwise noted)

100.0 100.0 90.0 90.0 IOUT=10mA VIN=5V IOUT=100mA IOUT=500mA 80.0 80.0 70.0 70.0 Efficiency (%) Efficiency (%) 60.0 60.0 50.0 50.0 VIN=17V IOUT=1mA 40.0 40.0 VIN=12V 30.0 30.0 20.0 20.0 10.0 10.0 0.0 0.0 0.001 0.01 5 10 11 12 15 0.1 3 4 6 9 13 14 16 8 17 1 Output Current (A) Input Voltage (V) G001 G001 Vout = 0.9 VVout = 0.9 VFigure 12. Efficiency versus Output Current Figure 13. Efficiency versus Input Voltage 3.35 3.35 IOUT=1mA IOUT=10mA Output Voltage (V) Output Voltage (V) 3.30 3.30 -----VIN=5V VIN=12V VIN=17 IOUT=100mA IOUT=500mA 1111 1110 3.25 3.25 3.20 0.0001 3.20 0.001 10 0.01 0.1 4 7 13 16 Output Current (A) Input Voltage (V) G001 G00<sup>-</sup> Figure 14. Output Voltage Accuracy (Load Regulation) Figure 15. Output Voltage Accuracy (Line Regulation) 4 4 3.5 3.5 Switching Frequency (MHz) Switching Frequency (MHz) 3 3 2.5 2.5 2 2 IOUT=0.5A 1.5 1.5 1 1 0.5 0.5 0 0 0 0.1 0.2 0.3 0.4 0.5 4 6 8 10 12 14 16 18 Output Current (A) Input Voltage (V) G000 G000 Figure 16. Switching Frequency versus Output Current Figure 17. Switching Frequency versus Input Voltage

#### At V\_{IN} = 12 V, V\_{OUT} = 3.3 V, and T\_J = 25°C (unless otherwise noted)

## TPS62170-Q1, TPS62171-Q1, TPS62172-Q1

SLVSCK7E - DECEMBER 2014-REVISED MAY 2020

At  $V_{\text{IN}}$  = 12 V,  $V_{\text{OUT}}$  = 3.3 V, and  $T_{\text{J}}$  = 25°C (unless otherwise noted)

## TPS62170-Q1, TPS62171-Q1, TPS62172-Q1

SLVSCK7E – DECEMBER 2014 – REVISED MAY 2020

At V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 3.3 V, and T<sub>J</sub> = 25°C (unless otherwise noted)

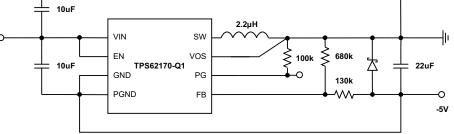

## 9.3 System Examples

## 9.3.1 Inverting Power Supply

The TPS62170-Q1 can be used as inverting power supply by rearranging external circuitry as shown in Figure 30. Since the former GND node now represents a voltage level below system ground, the voltage difference between  $V_{IN}$  and  $V_{OUT}$  has to be limited for operation to the maximum supply voltage of 17 V (see Equation 13).

$$V_{IN} + |V_{OUT}| \le V_{IN max}$$

$$(13)$$

Figure 30. –5-V Inverting Power Supply

The transfer function of the inverting power supply configuration differs from the buck mode transfer function, incorporating a Right Half Plane Zero additionally. The loop stability has to be adapted and an output capacitance of at least 22  $\mu$ F is recommended. A detailed design example is given in the Using the TPS6215x in an Inverting Buck-Boost Topology Application Report.

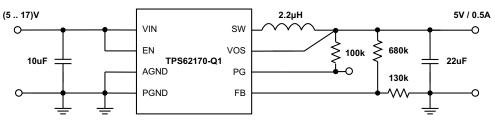

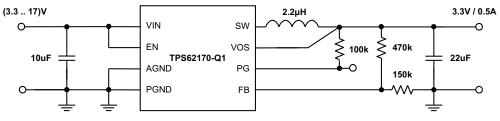

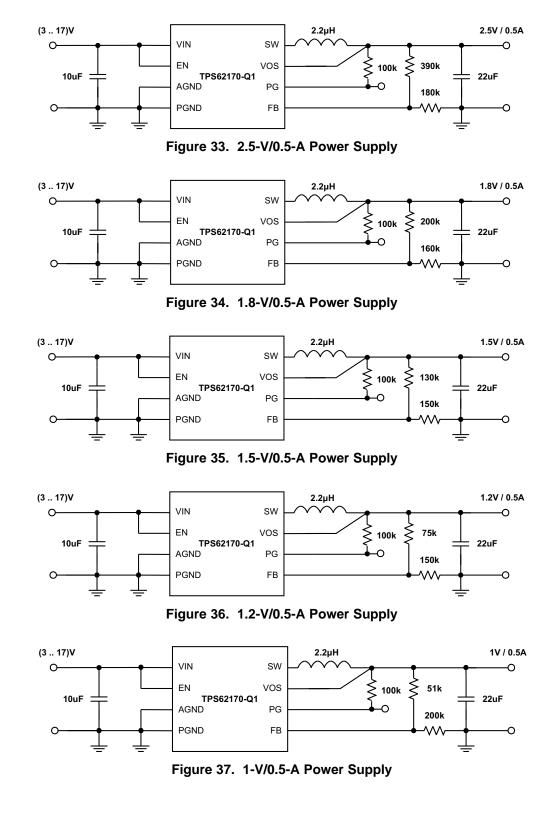

### 9.3.2 Various Output Voltages

The TPS62170-Q1 can be set for different output voltages between 0.9 V and 6 V. Some examples are shown below.

Figure 31. 5-V/0.5-A Power Supply

Figure 32. 3.3-V/0.5-A Power Supply

## System Examples (continued)

# **10 Power Supply Recommendations**

The TPS6217x-Q1 are designed to operate from a 3-V to 17-V input voltage supply. The output current of the input power supply needs to be rated according to the output voltage and the output current of the power rail application.

# 11 Layout

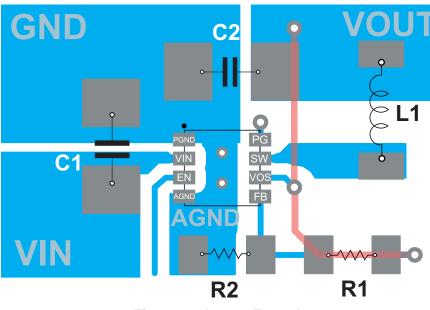

## 11.1 Layout Guidelines

A proper layout is critical for the operation of a switched mode power supply, even more at high switching frequencies. Therefore, the PCB layout of the TPS6217x-Q1 demands careful attention to ensure operation and to get the performance specified. A poor layout can lead to issues like poor regulation (both line and load), stability and accuracy weaknesses, increased EMI radiation, and noise sensitivity. Considering the following topics ensures best electrical and optimized thermal performance:

- 1. The input capacitor must be placed as close as possible to the VIN and PGND pin of the IC. This provides low resistive and inductive path for the high di/dt input current.

- 2. The VOS pin must be connect in the shortest way to VOUT at the output capacitor, avoiding noise coupling.

- 3. The feedback resistors, R1 and R2 must be connected close to the FB and AGND pins, avoiding noise coupling.

- 4. The output capacitor mst be placed such that its ground is as close as possible to the PGND pins of the IC, avoiding additional voltage drop in traces.

- 5. The inductor must be placed close to the SW pin and connect directly to the output capacitor, minimizing the loop area between the SW pin, inductor, output capacitor, and PGND pin.

More detailed information can be found in the TPS62160EVM-627 and TPS62170EVM-627 Evaluation Modules User's Guide.

The Exposed Thermal Pad must be soldered to the circuit board for mechanical reliability and to achieve appropriate power dissipation. Although the Exposed Thermal Pad can be connected to a floating circuit board trace, the device will have better thermal performance if it is connected to a larger ground plane. The Exposed Thermal Pad is electrically connected to AGND.

## 11.2 Layout Example

Figure 38. Layout Example

## 11.3 Thermal Considerations

Implementation of integrated circuits in low-profile and fine-pitch surface-mount packages typically requires special attention to power dissipation. Many system-dependent issues such as thermal coupling, airflow, added heat sinks and convection surfaces, and the presence of other heat-generating components affect the power-dissipation limits of a given component.

## **Thermal Considerations (continued)**

The following are three basic approaches for enhancing thermal performance:

- Improving the power dissipation capability of the PCB design

- Improving the thermal coupling of the component to the PCB by soldering the Exposed Thermal Pad

- Introducing airflow in the system

For more details on how to use the thermal parameters, see the *Thermal Characteristics* of *Linear and Logic Packages Using JEDEC PCB Designs Application Report* and *Semiconductor and IC Package Thermal Metrics Application Report*.

The TPS6217x-Q1 are designed for a maximum operating junction temperature  $(T_J)$  of 125°C. Therefore, the maximum output power is limited by the power losses that can be dissipated over the actual thermal resistance, given by the package and the surrounding PCB structures. Since the thermal resistance of the package is fixed, increasing the size of the surrounding copper area and improving the thermal connection to the IC can reduce the thermal resistance. To get an improved thermal behavior, it is recommended to use top layer metal to connect the device with wide and thick metal lines. Internal ground layers can connect to vias directly under the IC for improved thermal performance.

If short circuit or overload conditions are present, the device is protected by limiting internal power dissipation.

# 12 Device and Documentation Support

## 12.1 Device Support

## 12.1.1 Development Support

## 12.1.1.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the TPS62170-Q1 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage ( $V_{IN}$ ), output voltage ( $V_{OUT}$ ), and output current ( $I_{OUT}$ ) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

## 12.1.2 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

# **12.2 Documentation Support**

## 12.2.1 Related Documentation

- Optimizing the TPS62130/40/50/60/70 Output Filter Application Report

- Optimizing Transient Response of Internally Compensated dc-dc Converters With Feedforward Capacitor Application Report∖

- Using a Feedforward Capacitor to Improve Stability and Bandwidth of TPS62130/40/50/60/70 Application

Report

- Using the TPS6215x in an Inverting Buck-Boost Topology Application Report

- TPS62160EVM-627 and TPS62170EVM-627 Evaluation Modules User's Guide

- Thermal Characteristics of Linear and Logic Packages Using JEDEC PCB Designs Application Report

- Semiconductor and IC Package Thermal Metrics Application Report

## 12.3 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

| PARTS       | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL<br>DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |

|-------------|----------------|--------------|------------------------|---------------------|---------------------|

| TPS62170-Q1 | Click here     | Click here   | Click here             | Click here          | Click here          |

| TPS62171-Q1 | Click here     | Click here   | Click here             | Click here          | Click here          |

| TPS62172-Q1 | Click here     | Click here   | Click here             | Click here          | Click here          |

#### Table 4. Related Links

## 12.4 Trademarks

DCS-Control, E2E are trademarks of Texas Instruments. WEBENCH is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners.

## 12.5 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 12.6 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 12.7 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 12.8 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## PACKAGING INFORMATION

| Orderable Device | Status | Package Type | •       | Pins | Package | Eco Plan     | Lead finish/  | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|--------------|---------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)          | Ball material | (3)                 |              | (4/5)          |         |

|                  |        |              |         |      |         |              | (6)           |                     |              |                |         |

| TPS62170QDSGRQ1  | ACTIVE | WSON         | DSG     | 8    | 3000    | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | QUEQ           | Samples |

| TPS62170QDSGTQ1  | ACTIVE | WSON         | DSG     | 8    | 250     | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | QUEQ           | Samples |

| TPS62171QDSGRQ1  | ACTIVE | WSON         | DSG     | 8    | 3000    | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | QUFQ           | Samples |

| TPS62171QDSGTQ1  | ACTIVE | WSON         | DSG     | 8    | 250     | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | QUFQ           | Samples |

| TPS62172QDSGRQ1  | ACTIVE | WSON         | DSG     | 8    | 3000    | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | QUGQ           | Samples |

| TPS62172QDSGTQ1  | ACTIVE | WSON         | DSG     | 8    | 250     | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | QUGQ           | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPS62170-Q1, TPS62171-Q1, TPS62172-Q1 :

• Catalog: TPS62170, TPS62171, TPS62172

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

26-May-2020

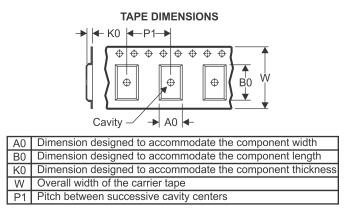

## TAPE AND REEL INFORMATION

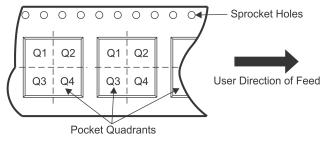

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS62170QDSGRQ1             | WSON            | DSG                | 8 | 3000 | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS62170QDSGTQ1             | WSON            | DSG                | 8 | 250  | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS62171QDSGRQ1             | WSON            | DSG                | 8 | 3000 | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS62171QDSGTQ1             | WSON            | DSG                | 8 | 250  | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS62172QDSGRQ1             | WSON            | DSG                | 8 | 3000 | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| TPS62172QDSGTQ1             | WSON            | DSG                | 8 | 250  | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

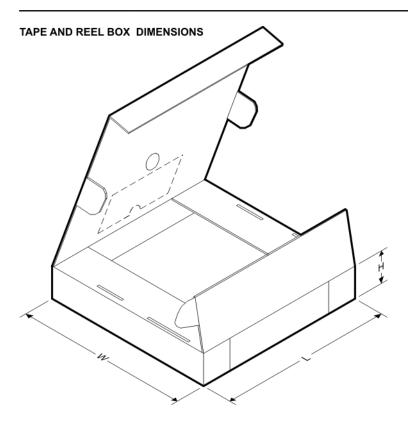

# PACKAGE MATERIALS INFORMATION

26-May-2020

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS62170QDSGRQ1 | WSON         | DSG             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS62170QDSGTQ1 | WSON         | DSG             | 8    | 250  | 210.0       | 185.0      | 35.0        |

| TPS62171QDSGRQ1 | WSON         | DSG             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS62171QDSGTQ1 | WSON         | DSG             | 8    | 250  | 210.0       | 185.0      | 35.0        |

| TPS62172QDSGRQ1 | WSON         | DSG             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS62172QDSGTQ1 | WSON         | DSG             | 8    | 250  | 210.0       | 185.0      | 35.0        |

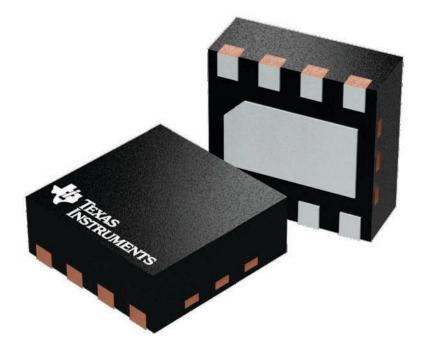

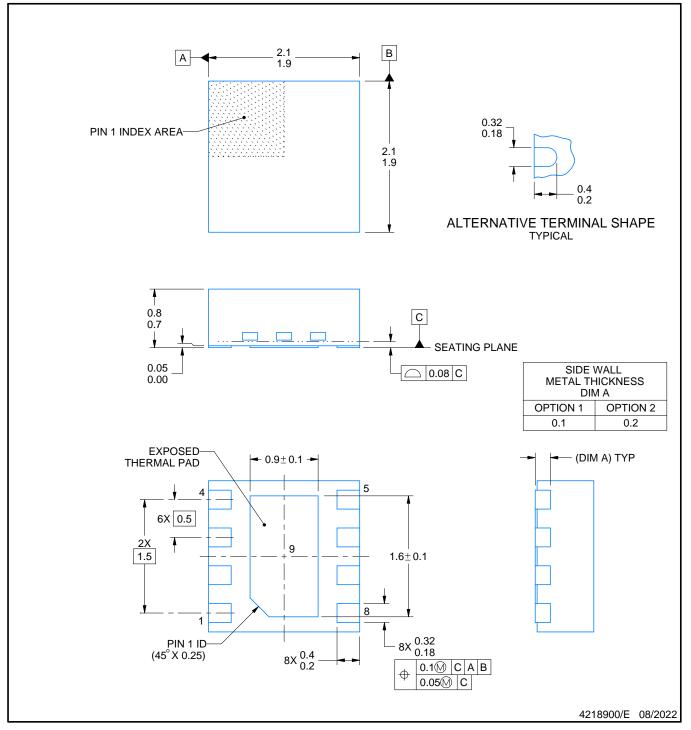

# DSG 8

2 x 2, 0.5 mm pitch

# **GENERIC PACKAGE VIEW**

# WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

# DSG0008A

# **PACKAGE OUTLINE**

# WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

# **DSG0008A**

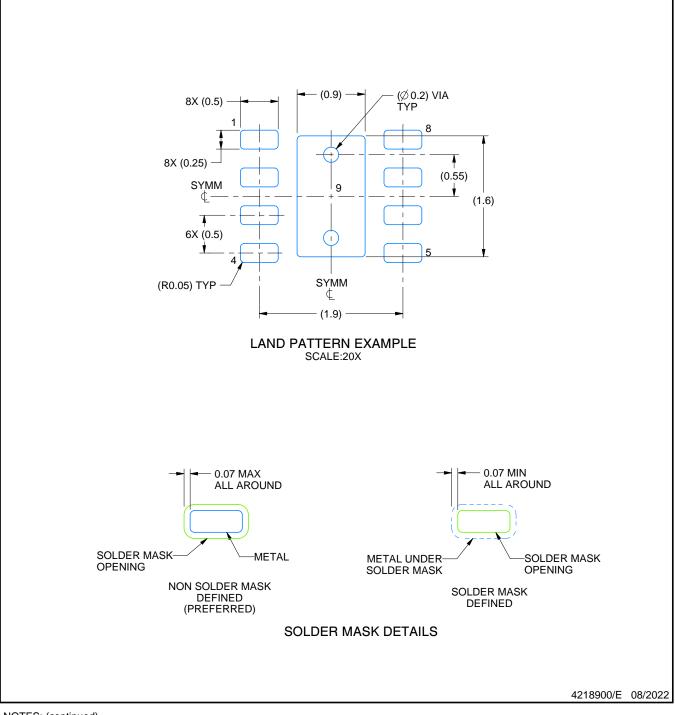

# **EXAMPLE BOARD LAYOUT**

# WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# **DSG0008A**

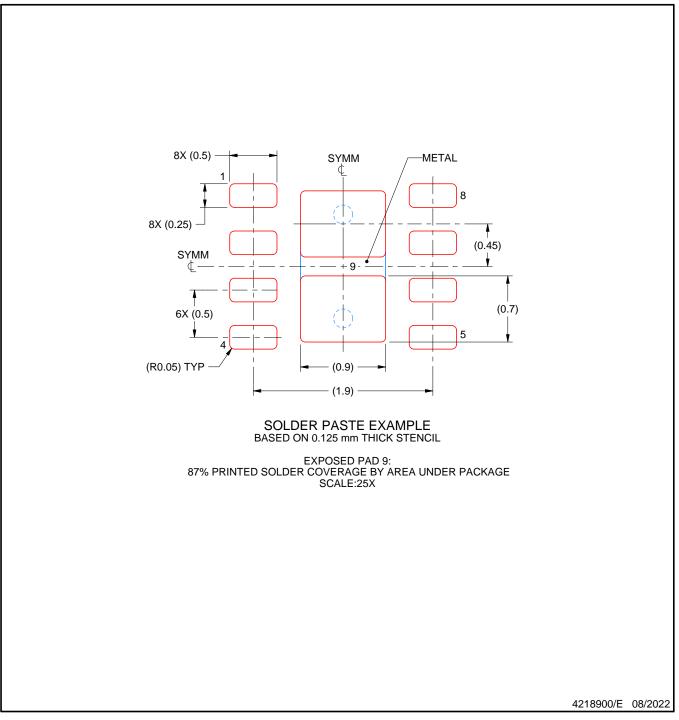

# **EXAMPLE STENCIL DESIGN**

# WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.