# 8-Port IEEE 802.3af/at PSE Controller for Power-over-Ethernet

### **Features**

- IEEE 802.3af/at compliant

- Single DC power supply voltage input (44~57V)

- Supplies 8 independent power ports

- Supports DC Load-Removal Detections

- Built-in power FETs

- 0.1Ω Sense embedded

- Up to 50W per Port for PSE Applications

- Wide temperature range: -40°C ~+85°C

- 9-Bit Port Current and Voltage Monitoring

- I<sup>2</sup>C Bus to access up to 8 x TMI7608S devices

- Independent system parameters setting for every port

- Thermal monitoring and protection

- Built-in 3.3V regulators for external devices

- Built-in Power on Reset

- Configurations: 30W x 8ports

- Built-in LEDs control for multi-port use

- Built-in EEPROM interface for dumb application

- Overload LED

- Pin Selectable Detection Backoff Timer for ALT A/B

- 2-Event Pin-Select

- Support 24V low voltage application

- Pin Programmable Maximum Total current limit for Smart power management.

- Robust Short-Circuit Protection

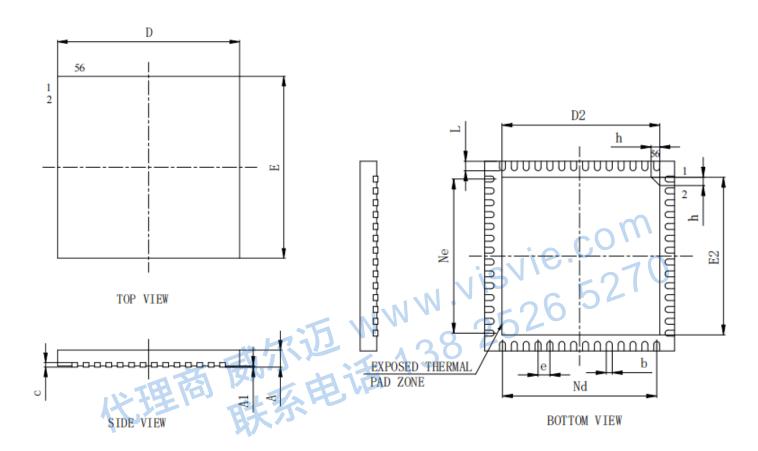

- Space-Saving,56-Pin QFN (8mm x 8mm)

Power Package

# **Application**

- PSE-ICM

- Power-Sourcing Equipment (PSE)

- Switches/Routers

- ALT A/B Power Injectors

# **Description**

TMI7608S is an 8-port PSE (Power Sourcing Equipment) controller IC for PoE (Power over Ethernet) systems. It integrates power, analog and logic circuits into a single chip, and can be used for Endpoint PSE Midspans and applications. TMI7608S meets all IEEE 802.3AF-2003 requirements, such as multi-point resistor detection, PD classification, DC Disconnect, and Back-off for Midspans. It also meets all IEEE 802.3AT-2009 requirements, such as two-event classification and supply maximum 36W per port. The device also supports Class4+ for detection and classification of high-power PDs. The device supports singlesupply operation, provides up to 50W to each port (Class4+ enabled).

TMI7608S comprises internal temperature monitoring and thermal protection to protect against junction overheating.

TMI7608S has a maximum power setting pin. Connect a resistor from this pin to AGND to set the total power capability on all 8 output ports. TMI7608S will limit the total power on 8 ports below this power limit.

The 3.3V regulator is built-in to support external devices. Multiple TMI7608Ss can integrate to build an 8 x N ports PSE system, and I<sup>2</sup>C bus uses to collect PD power status from each TMI7608S to support global power managements. Management switch host has options to communicate TMI7608S via I<sup>2</sup>C bus for PSE management activities. Optocouplers can be implemented to provide electrical isolations between the host and TMI7608S for signal communication.

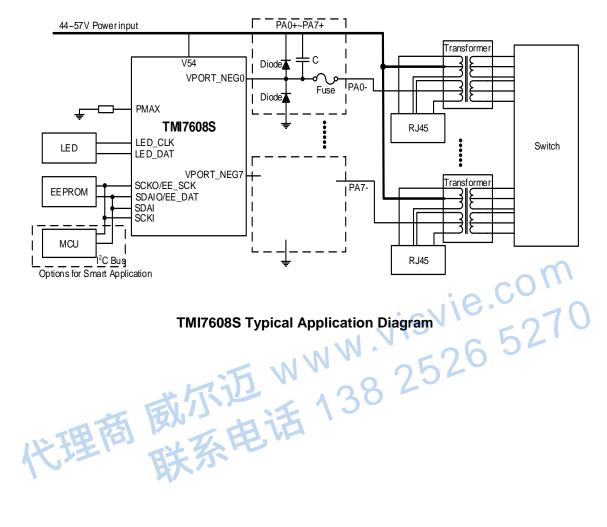

# **Typical Application**

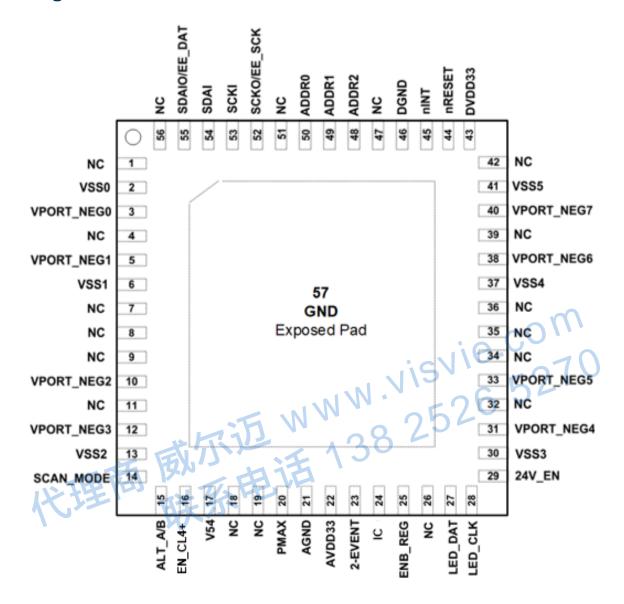

# **Package**

**Top View**

QFN8x8-56

Top Marking: T7608S/XXXXX (T7608S: Device Code, XXXXX: Inside Code)

# **Order Information**

| Part Number | Package   | Top Marking     | Quantity/Reel |

|-------------|-----------|-----------------|---------------|

| TMI7608S    | QFN8x8-56 | T7608S<br>XXXXX | 3000          |

TMI7608S devices are Pb-free and RoHS compliant.

# **Pin Functions**

| Pin | Name       | Function                                                                                                                                                                                                                                                                                                                                                    |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | NC         | No internal connection.                                                                                                                                                                                                                                                                                                                                     |

| 2   | VSS0       | Analog ground.                                                                                                                                                                                                                                                                                                                                              |

| 3   | VPORT_NEG0 | PortN0 negative feeding voltage input.                                                                                                                                                                                                                                                                                                                      |

| 4   | NC         | No internal connection.                                                                                                                                                                                                                                                                                                                                     |

| 5   | VPORT_NEG1 | PortN1 negative feeding voltage input.                                                                                                                                                                                                                                                                                                                      |

| 6   | VSS1       | Analog ground.                                                                                                                                                                                                                                                                                                                                              |

| 7   | NC         | No internal connection.                                                                                                                                                                                                                                                                                                                                     |

| 8   | NC         | No internal connection.                                                                                                                                                                                                                                                                                                                                     |

| 9   | NC         | No internal connection.                                                                                                                                                                                                                                                                                                                                     |

| 10  | VPORT_NEG2 | PortN2 negative feeding voltage input.                                                                                                                                                                                                                                                                                                                      |

| 11  | NC         | No internal connection.                                                                                                                                                                                                                                                                                                                                     |

| 12  | VPORT_NEG3 | PortN3 negative feeding voltage input.                                                                                                                                                                                                                                                                                                                      |

| 13  | VSS2       | Analog ground.                                                                                                                                                                                                                                                                                                                                              |

| 14  | SCAN_MODE  | SCAN_MODE is internally pulled down to AGND. It should be connected to AGND for normal operation.                                                                                                                                                                                                                                                           |

| 15  | ALT_A/B    | This pin is latched upon power-on reset to define the ALT_A/B Type and is internally pulled downed to DGND.  0: ALT_A(Default) 1: ALT_B                                                                                                                                                                                                                     |

| 16  | EN_CL4+    | Class4+ Enable Input. Referenced to DGND. EN_CL4+ is internally pulled down to DGND. Leave unconnected to disable the classification for Class4+ devices (IEEE 802.3at-compliant mode). Connect EN_CL4+ to V3P3 to enable the classification of Class4+ devices. EN_CL4+ is latched in after the device is powered up or after a reset condition.           |

| 17  | V54        | Main power supply input for chip the 1uF capacitor should be added between V54 and AGND.                                                                                                                                                                                                                                                                    |

| 18  | NC         | No internal connection.                                                                                                                                                                                                                                                                                                                                     |

| 19  | NC         | No internal connection.                                                                                                                                                                                                                                                                                                                                     |

| 20  | PMAX       | Maximum loading power setting pin. Connect a $75k\Omega$ resistor from this pin to AGND to set the total power capability on all 8 output ports. TMI7608S will limit the total power on 8 ports below this power limit. The PMAX setting signal is latched in IC during IC is powered up or after a reset condition. $P_{max}=R_{max}*78uA*V54$             |

| 21  | AGND       | Analog ground.                                                                                                                                                                                                                                                                                                                                              |

| 22  | AVDD33     | Analog 3.3V Power. When EnB_Reg is connected to AGND, the built-in 3.3V regulator is active, and besides TMI7608S itself, AVDD33 can provide 3.3V (6mA) for external device. When EnB_Reg is connected to 3.3V, AVDD33 should be connected to an external power 3.3V (6mA minimum) for TMI7608S. A 4.7uF capacitor should be added between AVDD33 and AGND. |

www.toll-semi.com

# 拓尔微电子 TOLL Microelectronic

|     | electronic   |                                                                                                                                                                                                                |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin | Name         | Function                                                                                                                                                                                                       |

| 23  | 2-EVENT      | 2-Event Classification Select. Referenced to AGND. 2-EVENT is internally pulled up to the digital supply. Leave unconnected to enable 2-Event classification. Force low to disable the 2-Event classification. |

| 24  | IC           | eFuse power: Internally Connected. Leave unconnected.                                                                                                                                                          |

| 25  | EnB_Reg      | Enable/Disable the internal 3.3V regulator Please refer to pin description of AVDD33.EnB_Reg is internally pulled up to AVDD33.                                                                                |

| 26  | NC           | No internal connection.                                                                                                                                                                                        |

| 27  | LED_DAT      | Serial LED data output. This pin is internally pulled up to the DVDD33.                                                                                                                                        |

| 28  | LED_CLK      | Serial LED clock output.                                                                                                                                                                                       |

| 29  | 24V_EN       | This pin is latched upon power-on reset to define the 24V_En and is internally pulled downed to DGND.  0: Disable (Default) 1: Enable                                                                          |

| 30  | VSS3         | Analog ground.                                                                                                                                                                                                 |

| 31  | VPORT_NEG4   | PortN4 negative feeding voltage input.                                                                                                                                                                         |

| 32  | NC           | No internal connection.                                                                                                                                                                                        |

| 33  | VPORT_NEG5   | PortN5 negative feeding voltage input.                                                                                                                                                                         |

| 34  | NC           | No internal connection.                                                                                                                                                                                        |

| 35  | NC           | No internal connection.                                                                                                                                                                                        |

| 36  | NC           | No internal connection.                                                                                                                                                                                        |

| 37  | VSS4         | Analog ground.                                                                                                                                                                                                 |

| 38  | VPORT_NEG6   | PortN6 negative feeding voltage input.                                                                                                                                                                         |

| 39  | NC           | No internal connection.                                                                                                                                                                                        |

| 40  | VPORT_NEG7   | PortN7 negative feeding voltage input.                                                                                                                                                                         |

| 41  | VSS5         | Analog ground.                                                                                                                                                                                                 |

| 42  | NC           | No internal connection.                                                                                                                                                                                        |

| 43  | DVDD33       | Digital power 3.3V. Internally connected to AVDD33.                                                                                                                                                            |

| 44  | nRESET       | It is a low active signal to reset TMI7608S.                                                                                                                                                                   |

| 45  | nINT         | Interrupt output and low active                                                                                                                                                                                |

| 46  | DGND         | Digital ground, it should be connected to AGND.                                                                                                                                                                |

| 47  | NC           | No internal connection.                                                                                                                                                                                        |

| 48  | ADDR2        | I <sup>2</sup> C device address bus AD2.                                                                                                                                                                       |

| 49  | ADDR1        | I <sup>2</sup> C device address bus AD1.                                                                                                                                                                       |

| 50  | ADDR0        | I <sup>2</sup> C device address bus AD0.                                                                                                                                                                       |

| 51  | NC           | No internal connection.                                                                                                                                                                                        |

| 52  | SCKO/EE_SCK  | This pin is I2C clock output.                                                                                                                                                                                  |

| 53  | SCKI         | I <sup>2</sup> C serial clock input.                                                                                                                                                                           |

| 54  | SDAI         | I <sup>2</sup> C serial data output.                                                                                                                                                                           |

| 55  | SDAIO/EE_DAT | This pin is I2C serial data input and output.                                                                                                                                                                  |

| 56  | NC           | No internal connection.                                                                                                                                                                                        |

www.toll-semi.com

| 57 | EPAD | Exposed pad, it should be connected to AGND. |

|----|------|----------------------------------------------|

代理商 **威尔**迈 WWW. Visvie.com 代理商 **威尔**迈 当 138 2526 5270

# **Absolute Maximum Ratings (Note 1)**

| Items                        | Description                     | Min  | Тур | Max | Unit     |

|------------------------------|---------------------------------|------|-----|-----|----------|

| Supply Voltage               | V54-AGND                        | -0.3 |     | 90  | <b>V</b> |

| PortN0~PortN3                | PortNn-AGND @n=0~7              | -0.3 |     | 90  | V        |

| All other Pins               | All other Pin – (AGND, or DGND) |      |     | 6   | V        |

| DGND                         | DGND – AGND                     | -0.3 |     | 0.3 | V        |

| Maximum Junction Temperature |                                 |      |     | 150 | °C       |

| Storage Temperature Range    |                                 | -65  |     | 150 | °C       |

| Lead Temperature             | 30s, reflow                     |      |     | 260 | °C       |

| T <sub>A</sub>               | Operating Ambient Temperature   | -40  |     | 85  | °C       |

# ESD Rating (Note2)

| ESD Rating (          | Note2)                                                                          | 201     | U        |

|-----------------------|---------------------------------------------------------------------------------|---------|----------|

| Items                 | Description                                                                     | Value   | Unit     |

| V <sub>ESD_HBM</sub>  | Human Body Model (HBM) ANSI/ESDA/JEDEC JS-001-2017 Classification, Class: 2     | ±2000 Z | <b>V</b> |

| V <sub>ESD_CDM</sub>  | Charged Device Mode (CDM) ANSI/ESDA/JEDEC JS-002-2018 Classification, Class: C3 | ±1000   | V        |

| I <sub>LATCH-UP</sub> | JEDEC STANDARD NO.78E APRIL 2016<br>Temperature Classification,<br>Class: I     | ±200    | mA       |

JEDEC specification JS-001

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2: Devices are ESD sensitive. Handling precaution is recommended.

(V54 = 32V to 60V, AGND = DGND = 0V, TA = -40°C to +85°C. All voltages are referenced to AGND, unless otherwise noted. Typical values are at V54 = 54V, TA = +25°C, and default register settings. Currents are positive when entering the pin, and negative otherwise.)

| Symbol                 | Description                                   | Conditions                                                    | Min  | Тур  | Max  | Units |

|------------------------|-----------------------------------------------|---------------------------------------------------------------|------|------|------|-------|

| POWER S                | UPPLIES                                       |                                                               |      |      |      |       |

| \                      | D 0 1 11                                      | 45V~57V @IEEE802.3af                                          | 32   |      | 60   | V     |

| V54                    | Power Supply voltage                          | 51V~57V @IEEE802.3at                                          | 50   |      | 60   | V     |

| 154                    | V54 operating current                         | All ports on @w/o peripheral load current & port load current |      | 8    | 10   | mA    |

| $V_{3P3}$              | AVDD33 voltage                                | IV3P3=0~10mA                                                  | 3    | 3.30 | 3.6  | V     |

| V <sub>3P3_UVLO</sub>  | AVDD33 Undervoltage<br>Lockout                |                                                               |      | 2    |      | V     |

| VELDI ST               | Foldback Initial Voltage                      | VPortN AGND above which the current-limit trip                | e.   | 32   | m    | V     |

| V <sub>FLBK_</sub> ST  | i oldback illitial voltage                    | voltage starts folding back                                   | 6    | 18   | 7    | V     |

| $V_{FLBK\_END}$        | Foldback Final Voltage                        | V54 - VPortN_ above which the current limit reaches VTH_FB    |      | 46   |      | V     |

| I <sub>LIM-TH_FB</sub> | Minimum Foldback<br>Current-Limit Threshold   | VPortN_= V54 = 57V                                            |      | 120  |      | mA    |

| 14                     | RS_ Input Bias Current                        | VRS_= AGND                                                    |      |      | -2   | μA    |

| I <sub>Inrush</sub>    | Output current in POWER_UP State              |                                                               | 400  |      | 450  | mA    |

|                        |                                               | Class0~3                                                      | 400  |      | 500  |       |

| $I_{LIM}$              | Short Circuit Current Limit Threshold(Note 3) | Class4                                                        | 750  |      | 1000 | mA    |

|                        | Trin contact cy                               | Class4+                                                       |      |      | 2000 |       |

|                        |                                               | Class0                                                        | 350  | 375  | 400  |       |

|                        |                                               | Class1                                                        | 91   | 112  | 133  | -     |

|                        | Overcurrent Threshold                         | Class2                                                        | 160  | 206  | 252  | mA    |

| I <sub>CUT</sub>       | after Startup                                 | Class3                                                        | 350  | 375  | 400  |       |

|                        |                                               | Class4                                                        | 600  | 640  | 680  |       |

|                        |                                               | Class4+                                                       | 1200 | 1280 | 1360 | -     |

(V54 = 32V to 60V, AGND = DGND = 0V, TA = -40°C to +85°C. All voltages are referenced to AGND, unless otherwise noted. Typical values are at V54 = 54V, TA = +25°C, and default register settings. Currents are positive when entering the pin, and negative otherwise.)

|                        | otilei wise.)                          |                                                                                                                                 |     |       |          |    |

|------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-------|----------|----|

| SUPPLY N               | MONITORS                               |                                                                                                                                 |     |       |          |    |

| $V_{UVLO}$             | V54 Undervoltage Lockout               | V54-AGND, V54-AGND increasing                                                                                                   |     | 30    |          | V  |

| V <sub>UVLO_H</sub>    | V54 Undervoltage Lockout<br>Hysteresis | Ports shut down if: V54 - AGND<br>< AGND_UVLO - AGND_UVLOH                                                                      |     | 3     |          | V  |

| T <sub>SHD</sub>       | Thermal-Shutdown<br>Threshold          | Port is shut down and device resets if the junction temperature exceeds this limit, temperature increasing (test mode) (Note 4) |     | 150   |          | °C |

| T <sub>SHDN</sub>      | Thermal-Shutdown<br>Hysteresis         | Temperature decreasing (Note 4)                                                                                                 |     | 20    |          | °C |

| PortN MO               |                                        |                                                                                                                                 |     |       | <u> </u> |    |

| _                      |                                        | VPortN_ = V54, during idle                                                                                                      |     |       | 2        | μA |

| BPortN                 | PortN_ Input Current                   | V54 - AGND = 48V, VPortN_ = AGND, during idle                                                                                   |     | 201   | -70      | μΑ |

| $R_{\text{DIS}}$       | Idle Pullup Resistance at<br>PortN_    | Detection and classification off, port shut down                                                                                | 0.7 | 1.    | 1.25     | МΩ |

| $P_{GTH}$              | PGOOD High Threshold                   | VPortN AGND, PortN_ decreasing                                                                                                  | 1.5 | 2     | 2.5      | V  |

| $P_{GHYS}$             | PGOOD Hysteresis                       | - MW 057                                                                                                                        | O   | 220   |          | mV |

| t <sub>PGOOD</sub>     | PGOOD Low-to-High<br>Glitch Filter     | Time VPortN AGND has to exceed PGTH to set the PGOOD_ bit in register 1Dh                                                       | 2   |       | 4        | ms |

| Total Load             | d Power Limit                          | 出语                                                                                                                              |     |       |          |    |

| 代                      | 埋" 联系                                  | RMAX = $19$ kΩ ( $18$ kΩ+ $1$ kΩ)<br>( $1$ max= $18$ μA*Rmax, V54= $18$ 4V)                                                     |     | 80    |          |    |

|                        | Load Power Limit on All 8<br>Ports     | RMAX = $28.5$ kΩ ( $27$ kΩ+ $1.5$ kΩ)                                                                                           |     | 120   |          |    |

| $P_{max}$              |                                        | RMAX = 38kΩ (36kΩ+2kΩ)                                                                                                          |     | 160   |          | W  |

|                        |                                        | RMAX =47.5kΩ                                                                                                                    |     | 200   |          |    |

|                        |                                        | RMAX =57kΩ (56kΩ+1kΩ)                                                                                                           |     | 240   |          |    |

| P <sub>MAX_LIMIT</sub> | Maximum Load Capability on all 8 Ports | Float PMAX pin (V54=54V)                                                                                                        |     | 430   |          | W  |

| T <sub>MAX-DLY</sub>   | Maximum Load Power                     | TPMAX bit=10 100% x PMAX <load <150%="" pmax<="" td="" x=""><td></td><td>60</td><td></td><td>ms</td></load>                     |     | 60    |          | ms |

| - WAX-DET              | Protection Delay                       | Load >150% x PMAX                                                                                                               |     | 1.024 |          | ms |

| LOAD DIS               | SCONNECT                               |                                                                                                                                 |     |       |          |    |

| I <sub>MPSTH</sub>     | DC Load Disconnect<br>Threshold        | Minimum Iport allowed before disconnect (DC disconnect active), VPortN_ = 0V                                                    | 5   | 7.5   | 10       | mA |

| t <sub>DISC</sub>      | Load Disconnect Time                   | Time from VRS_ < VDCTH to gate shutdown                                                                                         | 300 | 350   | 400      | ms |

|                        |                                        |                                                                                                                                 |     |       |          |    |

www.toll-semi.com

(V54 = 32V to 60V, AGND = DGND = 0V, TA = -40°C to +85°C. All voltages are referenced to AGND, unless otherwise noted. Typical values are at V54 = 54V, TA = +25°C, and default register settings. Currents are positive when entering the pin, and negative otherwise.)

| negative (            | otnerwise.)                            |                                                                          |                                 |         |      |      |     |

|-----------------------|----------------------------------------|--------------------------------------------------------------------------|---------------------------------|---------|------|------|-----|

| DETECTION             | ON                                     |                                                                          |                                 |         |      |      |     |

| V <sub>DPH1</sub>     | Detection Probe Voltage (First Phase)  | V54 - VDET during the first detection phase                              |                                 |         | 4    | 4.2  | V   |

| $V_{DPH2}$            | Detection Probe Voltage (Second Phase) | V54 - VDET during the seco<br>phase                                      | nd detection                    | 8.6     | 9    | 9.4  | V   |

| I <sub>DLIM</sub>     | Current-Limit Protection               | VPortN_ = V54, current mea<br>PortN_ during detection                    | _                               | 1.5     |      | 2    | mA  |

| V <sub>DCP</sub>      | Short-Circuit Threshold                | If V54 - VPortN_ < VDCP aft<br>detection phase, a short circ<br>detected |                                 |         | 1.5  |      | V   |

| I <sub>D_OPEN</sub>   | Open-Circuit Threshold                 | First point measurement cur<br>for open condition                        | rent threshold                  |         | 12.5 |      | μΑ  |

| R <sub>DOK</sub>      | Resistor Detection Window              | (Note 5)                                                                 |                                 | 19      |      | 26.5 | kΩ  |

| R <sub>DBAD</sub>     | Resistor Rejection Window              | Detection rejects lower value                                            | es                              |         |      | 15.2 | kΩ  |

| NDBAD                 | Resistor Rejection Window              | Detection rejects higher values                                          |                                 | 32      |      | 10   | K12 |

| CLASSIFI              | CATION                                 |                                                                          | visy,                           |         | -0   | 70   |     |

| V <sub>CL</sub>       | Classification Probe<br>Voltage        | V54 - VPortN_ during classi                                              | fication                        | 15.5    | 2    | 20   | V   |

| I <sub>CL_LIM</sub>   | Current-Limit Protection               | VPortN_ = V54, current mea<br>PortN                                      | 60                              | 70      | 80   | mA   |     |

| t <sub>CL_E</sub>     | Classification Event Timing            | 二注 130                                                                   |                                 | 14      | 18   | 22   | ms  |

| V <sub>MARK</sub>     | Mark Event Voltage                     | V54 - VDET during mark eve                                               | ent                             | 8       |      | 9.6  | V   |

| I <sub>MARK_LIM</sub> | Mark Event Current Limit               | VDET = V54, during mark ev<br>current through DET                        | vent measure                    | 34      | 40   | 46   | mA  |

| t <sub>MARK_E</sub>   | Mark Event Timing                      |                                                                          |                                 | 7       | 9    | 11   | ms  |

|                       |                                        |                                                                          | Class 0,<br>Class 1             | 5       | 6.5  | 8    |     |

|                       |                                        |                                                                          | Class 1,<br>Class 2             | 13 14.5 |      | 16   |     |

| I <sub>CL</sub>       | Classification Current<br>Thresholds   | Classification current thresholds between classes                        | Class 2,<br>Class 3             | 21      | 23   | 25   | mA  |

|                       |                                        |                                                                          | Class 3,<br>Class 4             | 31      | 33   | 35   |     |

|                       |                                        |                                                                          | Class 4 upper<br>limit (Note 6) | 45      | 48   | 51   |     |

(V54 = 32V to 60V, AGND = DGND = 0V, TA = -40°C to +85°C. All voltages are referenced to AGND, unless otherwise noted. Typical values are at V54 = 54V, TA = +25°C, and default register settings. Currents are positive when entering the pin, and negative otherwise.)

|                      | otnerwise.)<br>INPUTS/OUTPUTS (Voltage     | es Referenced to AGND)                                                                          |     |      |               |    |

|----------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------|-----|------|---------------|----|

| V <sub>IL</sub>      | Digital Input Low                          | ,                                                                                               |     |      | 0.8           | V  |

| V <sub>IH</sub>      | Digital Input High                         |                                                                                                 | 2   |      |               | V  |

| $R_{\text{DIN}}$     | Internal Input<br>Pullup/Pulldown Resistor | Pullup (pulldown) resistor to V3P3 (DGND) to set default level                                  | 25  | 50   | 75            | kΩ |

| $V_{\text{OL}}$      | Open-Drain output Low<br>Voltage           | ISINK = 10mA                                                                                    |     |      | 0.4           | V  |

| $I_{OL}$             | Open-Drain Leakage                         | Open-drain high impedance, VPortN_ = 3.3V                                                       |     |      | 1             | μΑ |

| I <sub>DL</sub>      | SCL, SDAIN Input<br>Leakage                | Input connected to the pull voltage                                                             |     |      | 1             | μA |

|                      | Hardware Reset Pulse<br>Width              | Minimum low pulse duration on nRESET to lead to a hardware reset event                          | 120 | -01  | $\mathcal{M}$ | μs |

| TIMING               |                                            |                                                                                                 | 0.  | CO   |               |    |

| t <sub>START</sub>   | Startup Time                               | Time during which a current limit set by VSU_LIM is allowed, starts when the GATE_ is turned on | 50  | 60   | 70            | ms |

| t <sub>FAULT</sub>   | Fault Time                                 | Time allowed for an evergurrent fault get                                                       |     | 60   | 70            | ms |

| $t_{LIM}$            | Current Limit                              | Time during after startup (Note 7)                                                              | 50  | 60   | 70            | ms |

| t <sub>OFF</sub>     | Port_Turn-Off Time                         | Minimum delay between any port turn-off, does not apply in a reset case                         |     | 0.1  |               | ms |

| Ron                  | Port on resistance                         | lport ≦ 640mA, & Ta=25°C                                                                        |     | 0.15 |               | Ω  |

| 1                    | Detection Reset Time                       | Time allowed for the port voltage to reset before detection starts                              |     | 800  |               | ms |

| t <sub>DET</sub>     | Detection Time                             | Maximum time allowed before detection is completed                                              |     |      | 330           | ms |

| t <sub>DMID</sub>    | ALT_A/B Mode Detection Delay               |                                                                                                 | 2   |      |               | s  |

| $t_{\text{CLASS}}$   | Classification Time                        | Time allowed for classification                                                                 |     | 19   | 25            | ms |

| t <sub>DLY</sub>     | V54_UVLO Turn-On Delay                     | Time V54 must be above the V54_UVLO threshold before the device operates                        | 2   |      | 4             | ms |

| t <sub>RESTART</sub> | Restart Timer                              | Time the device waits before turning on after an overcurrent fault, ALT_A/B disabled            |     | 2    | 2.4           | s  |

(V54 = 32V to 60V, AGND = DGND = 0V, TA = -40°C to +85°C. All voltages are referenced to AGND, unless otherwise noted. Typical values are at V54 = 54V, TA = +25°C, and default register settings. Currents are positive when entering the pin, and negative otherwise.)

| ADC PER              | RFORMANCE (Power-On M                            | oae)               |                     |       |          |      |      |

|----------------------|--------------------------------------------------|--------------------|---------------------|-------|----------|------|------|

|                      | Resolution                                       |                    |                     |       | 9        |      | Bits |

|                      | Offset Error                                     | Voltage reading    | TA = -40°C to +85°C |       |          | 3    | LSB  |

|                      | Oliset Liloi                                     | Current reading    | TA = -40°C to +85°C |       |          | 3    | LOD  |

|                      | Gain Error                                       | Gain error voltage | TA = -40°C to +85°C | -2.5  |          | 2.5  | %    |

|                      | Gain Life                                        | Gain error current | 1A = -40 C to 100 C | -2.5  |          | 2.0  | 70   |

|                      | V54 Voltage Accuracy                             | V54-AGND=48V       | TA = -40°C to +85°C | -2.5  |          | 2.5  | %    |

| I <sub>NL</sub>      | Integral Nonlinearity                            |                    |                     |       |          | 1    | LSB  |

| $D_NL$               | Differential Nonlinearity                        |                    |                     |       |          | 1    | LSB  |

|                      | Current Pending Pange                            | Classes 0-4        |                     |       | <b>1</b> |      | Α    |

|                      | Current Reading Range                            | Class4+            |                     | 1.9   | 2        | 10   | A    |

|                      | Command I CD Ctan Cina                           | Classes 0-4        | , 11151             |       | 1.956    |      | A    |

|                      | Current LSB Step Size                            | Class4+            |                     | 6     | 3.912    |      | mA   |

|                      | Voltage Reading Range                            | All Classes        | 0756                |       | 63.6     |      | V    |

|                      | Voltage LSB Step Size                            | All Classes        | 30                  |       | 124.5    |      | mv   |

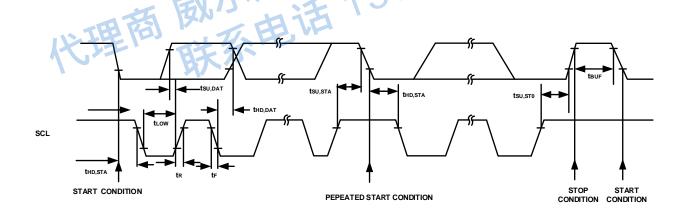

| IMING C              | CHARACTERISTICS                                  | 4175               |                     |       |          |      |      |

| fscL                 | Serial Clock Frequency                           | PO"                |                     | 1     |          | 1000 | kHz  |

| t <sub>BUF</sub>     | Bus Free Time Between a STOP and START Condition |                    |                     | 0.125 |          |      | μs   |

| t <sub>HD, STA</sub> | Hold Time for a START Condition                  |                    |                     | 0.125 |          |      | μs   |

| $t_{LOW}$            | Low Period of the SCL<br>Clock                   |                    |                     | 0.25  |          |      | μs   |

| t <sub>HIGH</sub>    | High Period of the SCL<br>Clock                  |                    |                     | 0.25  |          |      | μs   |

|                      |                                                  | START and STOP     | conditions          | 0.125 |          |      |      |

| 4                    | Data in Hold Time                                | Receive            |                     | 0     |          |      | no   |

| t <sub>HD, DAT</sub> | Data in Hold Time                                | Transmit           |                     | 250   |          | 375  | ns   |

| t <sub>SU, DA</sub>  | Data in Setup Time                               |                    |                     | 125   |          |      | ns   |

| t <sub>LOW_EXT</sub> | Cumulative Clock Low Extend Time                 |                    |                     |       |          | 10   | ms   |

| t <sub>F</sub>       | Fall Time of SDAO Transmitting                   | (Note 8)           |                     |       |          | 250  | ns   |

| t <sub>SU, STO</sub> | Setup Time for STOP<br>Condition                 |                    |                     | 0     |          |      | μs   |

| t <sub>SP</sub>      | Pulse Width of Spike<br>Suppressed               | (Note 8)           |                     |       | 30       |      | ns   |

www.toll-semi.com

Production testing done at +25°C. Overtemperature limits are guaranteed by design and not production tested.

- **Note 3:** The current-limit thresholds are programmed through the I<sup>2</sup>C interface.

- Note 4: Functional test is performed over thermal shutdown entering test mode.

- **Note 5:** RDOK = (VPortN2 VPortN1) / (IPortN2 IPortN1). VPortN1, VPortN2, IPortN1, and IPortN2 represent the voltage at PortN\_ and the current into PortN\_ during phase 1 and 2 of the detection, respectively.

- **Note 6:** If Class4+ is enabled, this value is the classification current threshold from Class 4 to Class4+, and classification currents between 51mA and ICL\_LIM will be classified as Class4+.

- **Note 7:** Default value. The fault timer can be reprogrammed through the I<sup>2</sup>C interface (TLIM\_[3:0]).

- Note 8: Guaranteed by design. Not subject to production testing.

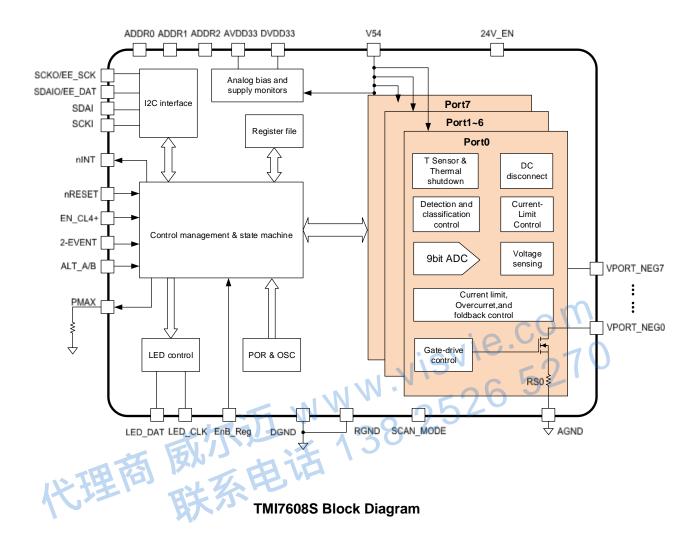

# **Block Diagram**

# **Functions Description**

### **Detailed Description**

The TMI7608S is an 8-port PSE power controller designed for use in IEEE 802.3at/af-compliant PSE. This device provides PD discovery, classification, current limit, and load disconnect detections. The device supports both fully automatic operation and software programmability. The device also supports 2-event classification and Class4+ for detection and classification of high-power PDs. The device supports single-supply operation, pro- vides up to 50W to each port (Class4+ enabled), and still provides high-capacitance detection for legacy PDs. The device features an I<sup>2</sup>C -compatible is fully software configurable and programmable. The device provides instantaneous readout of port current and voltage through the I<sup>2</sup>C interface. The device provides input under-voltage lockout (UVLO), over-temperature protection, and output voltage slew-rate limit during startup.

#### Reset

The device is reset by any of the following conditions:

- 1) Power-up/down. Reset condition is asserted once V54 falls below the UVLO threshold.

- 2) Hardware reset. To initiate a hardware reset, pull nRESET low to DGND for at least 100µs. Hardware reset clears once, nRESET returns high to AVDD33, and all registers are set to their default states.

- 3) Software reset. To initiate a software reset, write a logical 1 to the RESET\_IC register (R2Bh[4]) any time after power-up. Reset clears automatically.

- 4) Thermal shutdown. The device enters thermal shut-down at +150°C. The device exits thermal shutdown and is reset once the temperature drops below 130°C.

During normal operation, changes to the address inputs, ALT\_A/B, EN\_CL4+, 2-EVENT and PMAX are ignored, and they can be changed at any time prior to a reset state. At the end of a reset event, the device latches in the state of these inputs.

#### **Port Reset**

Set RESET\_P\_ (R2Ah[7:0]) high anytime during normal powered operation to turn off port, disable detection and classification, and clear the Port Event and Status registers. If a port is not powered, setting RESET\_P\_ high for that port has no effect. Individual port reset does not initiate a global device reset.

### **ALT B Mode**

In ALT\_B mode, the device adopts cadence timing during the detection phase. When cadence timing is enabled and a failed detection occurs, the ports wait at least 2s before attempting to detect again. ALT\_B mode is activated by setting ALT\_A/B high and then powering or resetting the device. Alternatively, ALT\_B mode can be software programmed individually for each port by setting ALT\_B\_ (R24h[7:0]) to a logical 1. By default, the ALT\_A/B input is internally pulled downed to AGND to disable this function.

### Operation Modes

The device provides four operating modes to suit different system requirements. By default, auto mode allows the device to operate automatically at its default settings without any software. Semiautomatic mode automatically detects and classifies devices connected to the ports but does not power a port until instructed to by software. Manual mode allows total software control of the device and is useful for system diagnostics. Shutdown mode terminates all activities and securely turns off power to the ports.

Switching between auto, semiautomatic, and manual mode does not interfere with the operation of an out- put port. When a port is set into shutdown mode, all port operations are immediately stopped and the port remains idle until shutdown mode is exited.

### **Auto (Automatic) Mode**

By default, The device enters auto mode after power-up or when the reset condition is cleared. To manually place a port into auto mode from any other mode, set the corresponding port mode bits (R1Fh[7:0]/R20h[7:0) to [11]. In auto mode, the device performs detection, classification, and powers up the port automatically if a valid PD is connected to the port. If a valid PD is not connected at the port, the device repeats the detection routine continuously until a valid PD is connected. When entering auto mode after a reset condition, the DET\_EN\_(R22h[7:0]) and CLASS\_EN\_ bits (R23h[7:0]) are set to high and stay high, unless changed by software. When entering auto mode from any other mode due to a software command (programmed with R1Fh[7:0]/R20h[7:0]), the DET\_EN\_ and CLASS\_EN\_ bits retain their Semiautomatic (Semi) Mode

Enter semiautomatic mode by setting the port operating mode (R1Fh/R20h) to [10]. When entering semi mode, the DET\_EN\_ and CLASS\_EN\_ bits retain their previous states. When the DET\_EN\_ and/or CLASS EN bits are set to 1, the TMI7608S performs detection and/or classification repeatedly, but do not power up the port(s) automatically. Setting R28h[7:0] (PWR\_ON\_) high turns on power to the port(s) if detection and classification has successfully completed. If a port is powered down while in semiautomatic mode, the corresponding DET\_EN\_ and CLASS\_EN\_ bits are reset to 0.

#### Manual Mode

Enter manual mode by setting the port operating mode (R1Fh/R20h) to [01]. Manual mode allows the software to dictate any sequence of operation. In manual mode, the Detection/Classification register (R22h) is set to 00h, and DET\_EN\_/CLASS\_EN\_ become push-button bits. A port will only perform a single detection/classification cycle when DET\_EN\_/ CLASS\_EN\_ are set high, and they are reset low after execution.

PWR\_ON\_ (R28h[7:0]) has the highest priority, and setting PWR\_ON\_ high at any time causes the device to immediately enter the powered mode. Setting DET\_EN\_ and CLASS\_EN\_ high at the same time causes detection to be performed first. Once in the powered state, the device ignores DET\_EN\_ and CLASS EN commands.

#### **Shutdown Mode**

To put a port into shutdown mode, set the corresponding port mode bits (R1Fh/R20h) to [00]. Putting a port into shutdown mode immediately turns off port power, clears the event and status bits, and halts all port operations. In shutdown mode the serial interface is still fully active; however, all DET\_EN\_, CLASS\_EN\_, and PWR\_ON\_ commands are ignored.

#### **PD Detection**

During normal operation, the device probes the output for a valid PD. A valid PD has a 25kΩ discovery signature characteristic as specified in the IEEE 802.3at/af standard. Table 1 shows the IEEE 802.3at specification for a PSE detecting a valid PD signature. After each detection cycle, the device sets DET\_ (R06h[7:0] and R07h[7:0]) to 1 and reports the detection results in the detection status bits. The DET\_ bits are reset to 0 when read through the CoR (clear on read) register (R07h), or after a reset event. During detection, the device keeps the internal MOSFET off and forces two probe voltages through PortN\_. The current through PortN\_ is measured, as well as the voltage difference from AGND to PortN\_. A two point slope measurement is used, as specified by the IEEE 802.3at/ af standard, to verify the device connected to the port. The device implements appropriate settling times to reject 50Hz/60Hz power-line noise coupling. To prevent damage to non-PD devices, and to protect itself from an output short circuit, the device limits the current into PortN\_ to less than 2mA (max) during PD detection. In ALT\_B mode, after every failed detection cycle, the device waits at least 2.0s before attempting another detection cycle.

Table 1. PSE PI Detection Modes Electrical Requirements (IEEE 802.3at)

| PARAMETER                              | SYMBOL | MIN | MAX  | UNIT | ADDITIONAL INFORMATION                                |

|----------------------------------------|--------|-----|------|------|-------------------------------------------------------|

| Open-Circuit Voltage                   | VOC    | £ \ | 30   | V    | In detection mode only                                |

| Short-Circuit Current                  | ISC    | 1   | 5    | mA   | In detection mode only                                |

| Valid Test Voltage                     | VVALID | 2.8 | 10   | V    | _                                                     |

| Voltage Difference Between Test Points | △VTEST | 1   | _    | V    | _                                                     |

| Time Between Any Two Test<br>Points    | tBP    | 2   |      | ms   | This timing implies a 500Hz maximum probing frequency |

| Slew Rate                              | VSLEW  | _   | 0.1  | V/µs | _                                                     |

| Accept Signature Resistance            | RGOOD  | 19  | 26.5 | kΩ   | _                                                     |

| Reject Signature Resistance            | RBAD   | <15 | >33  | kΩ   | _                                                     |

| Open-Circuit Resistance                | ROPEN  | 500 |      | kΩ   | _                                                     |

| Accept Signature Capacitance           | CGOOD  |     | 150  | nF   | _                                                     |

| Reject Signature Capacitance           | CBAD   | 10  |      | μF   | _                                                     |

| Signature Offset Voltage Tolerance     | VOS    | 0   | 2.0  | V    | _                                                     |

| Signature Offset Current Tolerance     | IOS    | 0   | 12   | μΑ   | _                                                     |

### **Power Device Classification**

During PD classification, the device forces a probe voltage between 15V and 20V at PortN\_ and measures the current into PortN\_. The measured current determines the class of the PD.

After each classification cycle, the device sets CLS\_ (R08h[7:0] and R09h[7:0]) to 1 and reports the classification results in the classification status bits. The CLS\_ bits are reset to 0 when read through the CoR (clear on read) register (R09h) or after a reset event.

If EN\_CL4+ is left unconnected, the device will classify the PD based on IEEE 802.3at standard. If the measured current exceeds 51mA, the device will not power the PD, but will report an over- current classification result and will return to IDLE state before attempting a new detection cycle.

#### Class4+ PD Classification

The device supports high power beyond the IEEE802.3at standard by providing an additional classification (Class4+) if needed. To enable Class4+, connect EN\_CL4+ to V3P3 and initiate a global reset or use the soft- ware to individually enable Class4+ classification for each port (R2Dh[3:0]). Once Class4+ is enabled, during classification, if the device detects currents in excess of the Class 4 upper-limit threshold, the PD will be classified as a Class4+ powered device. The PD is guaranteed to be classified as a Class4+ device for any classification current from 51mA up to the classification current-limit threshold. The Class4+ overcurrent threshold and current limit will be set automatically with ICUT [5:0] and ILIM\_. Leave EN\_CL4+ unconnected to disable Class4+ detection and to be fully compliant to IEEE 802.3at standard classification.

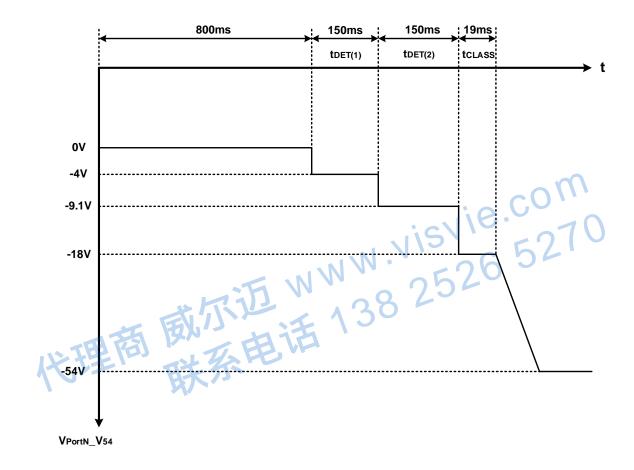

#### 2-Event PD Classification

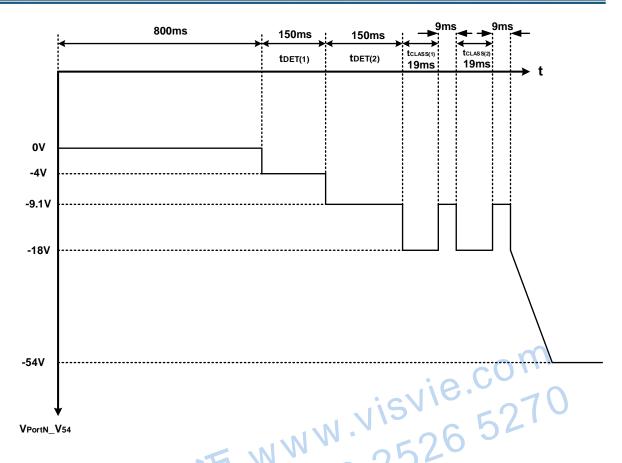

If the result of the first classification event is Class 0 to 3, then only a single classification event occurs as shown in Figure 1. However, if the result is Class 4 (or Class4+), the device will perform a second classification event as shown in Figure 2. Between the classification cycles, the device performs a first and the second mark event as required by the IEEE 802.3at standard, forcing a 9.1V probing voltage at PortN\_.

Figure 1. Detection, Classification, and Port Power-Up Sequence

Figure 2. Detection, 2-Event Classification, and Port Power-Up Sequence

### **Powered State**

When the device enters a powered state, the tFAULT timer is reset and power is delivered to the PD. PGOOD\_ (R1Dh[7:0]) is set to 1 when the device enters the normal power condition. PGOOD\_ immediately resets to 0 whenever the power to the port is turned off. The power-good change bits, PG\_CHG\_ (R02h[7:0]) are set both when the port powers up and when it powers down.

#### **Over current Protection**

During startup, if the current-limit condition persists, when the startup timer, tSTART, times out, the port shuts off, and the TSTART\_bit is set (R0Eh[7:0] and R0Fh[7:0]). In the normal powered state, the device checks for overcurrent conditions as determined by VCUT. The tFAULT counter sets the maximum allowed continuous current period.

When the counter reaches the tFAULT limit, the device powers the port down and asserts the corresponding TCUT\_ bit (R0Ah[7:0] and R0Bh[7:0]). For a continuous overstress, a fault latches exactly after a period of tFAULT. VCUT is programmable through the ICUT\_ registers. If a port is powered down due to a current-limit condition, during normal operation, the device asserts the corresponding ICV\_ bit (R10h[7:0] and R11h[7:0]) After power-off due to an overcurrent fault, the tFAULT timer is not immediately reset but starts decrementing at the same slower pace. The device allows a port to be powered on only when the tFAULT counter is at zero. This feature sets an automatic duty-cycle protection to the internal MOSFET to avoid overheating.

Table 2. PSE Classification of a PD (Table 33-9 of the IEEE 802.3at Standard)

| ,                    |                           |

|----------------------|---------------------------|

| MEASURED ICLASS (mA) | CLASSIFICATION            |

| 0 to 5               | Class 0                   |

| > 5 and < 8          | May be Class 0 or 1       |

| 8 to 13              | Class 1                   |

| > 13 and < 16        | Either Class 1 or 2       |

| 16 to 21             | Class 2                   |

| > 21 and < 25        | Either Class 2 or 3       |

| 25 to 31             | Class 3                   |

| > 31 and < 35        | Either Class 3 or 4       |

| 35 to 45             | Class 4                   |

| > 45 and < 51        | Either Class 4 or Invalid |

#### **Foldback Current**

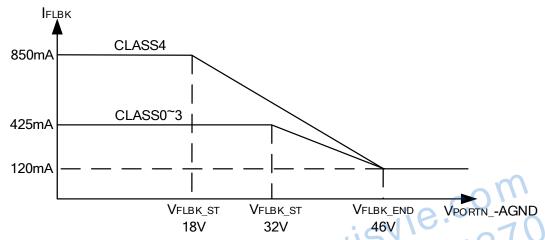

During startup and normal operation, an internal circuit senses the voltage at PortN\_ and when necessary reduces the current-limit clamp voltage (VSU\_LIM) to help reduce the power dissipation through the internal FET. When ILIM\_ = (Class 0–3), foldback begins when VPortN\_ - AGND > 32V; and when ILIM\_ = (Class 4 and 4+), foldback begins when VPortN\_ - AGND > 18V. The VSU\_LIM eventually reduces down to the minimum current-limit threshold VTH\_FB when VPortN\_ - AGND > 46V (Figure 3).

Figure 3. Foldback Current Characteristics

### Interrupt

The device contains an open-drain logic output (nINT)that goes low when an interrupt condition exists. The Interrupt register (R00h) contains the interrupt flag bits and the Interrupt Mask register (R01h) determines which events can trigger an interrupt. When an event occurs, the appropriate Interrupt Event register bits (in R02h to R13h) and the corresponding interrupt (in R00h) are set to 1 and nINT is asserted low (unless masked). If the master device on the I2C bus sends out an Alert Response Address, any TMI7608S device on the bus that has nINT asserted will respond. As a response to an interrupt, the controller can read the status of the event register(s) to determine the cause of the interrupt and take appropriate action. Each interrupt event register is paired with a Clear-on-Read (CoR) register. When an interrupt event register is read through the corresponding CoR register, the corresponding event register is reset to 0 (clearing interrupt event). nINT remains low and the interrupt is not reset when the Interrupt Event register is read through the read-only address. For example, to clear a supply event fault read R13h (CoR) not R12h (readonly). Use the INT\_CLR bit (R2Bh[7]) to clear an interrupt, or the RESET\_IC bit (R2Bh[4]) to initiate software resets.

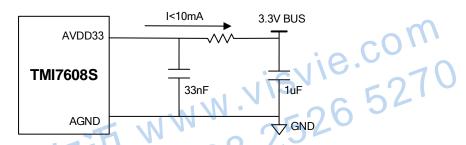

# **AVDD33 Power Supply**

The device has an internally regulator generates 3.3V power for internal use and 3.3V power also can supply typical 10mA current on V3P3 pin for external devices. V3P3 has an under-voltage lockout (V3P3\_UVLO) of 2V, and an under- voltage condition on V3P3 keeps the device in reset and the ports shut off. When V3P3 has recovered and the Reset condition clears, the V3P3\_UVLO bit in the Supply Event registers is set to 1 (R0Ah[12] and R0Bh[13]). The digital address inputs, and ALT\_A/B are internally pulled up to AVDD33, and all digital inputs are referenced to DGND. AVDD33 can also be used to source up to 6mA for external circuitry. For internal regulator stability, connect a 1uF capacitor in parallel with a 33nF capacitor at the AVDD33 output (Figure 4). If an external load is to be shared among multiple TMI7608S devices, isolate the external supply bus with a series resistor ( $50\Omega$  for 3 devices,  $75\Omega$  for 4 devices), and place a single 1uF capacitor on the bus.

In addition, the TMI7608S can also be powered by an external 3.3V connection to the AVDD33, and the EnB\_Reg must also be pulled up to 3.3V, which can reduce the power consumption and temperature rise of the device.

Figure 4 AVDD33 External Power Sourcing

## **Undervoltage Protection**

The device contains undervoltage protection features, and the flag bits can be found in the Supply Event register (R12h and R13h). An internal AGND undervoltage lockout circuit keeps the MOSFET off and the device in reset until V54 exceeds 30V for more than 3ms. An internal overvoltage circuit shuts down the ports. The digital supply also contains an undervoltage lockout that triggers when V3P3 - AGND  $\leq$  2V.

#### **DC Disconnect Monitoring**

The DC disconnect monitoring settings are found in the Disconnect Enable register (R21h). To enable DC disconnect, set either the DCD\_EN\_ bit for the corresponding port to 1. To disable the DC disconnect monitoring, DCD\_EN\_ bit for that port must be set to 0. When enabled, if VRSENSE\_ (the voltage across RSENSE\_) falls below the DC load disconnect threshold, VDCTH, for more than tDISC, the device turns off power and asserts the DIS \_\_\_\_\_ bit for the corresponding port (R0Ch[7:0] and R0Dh[7:0]).

#### **Hardware Power-Down**

The nRESET digital input is referenced to DGND and is used for hardware level control of device power management. During normal operation, nRESET should be externally pulled directly up to V3P3, the 3.3V internal regulator output. To initiate a hardware reset and port power-down, pull nRESET to DGND for at least 100µs. While nRESET is held low, the device remains in reset and the ports remain securely powered down. Normal device operation resumes once nRESET is pulled up to the V3P3.

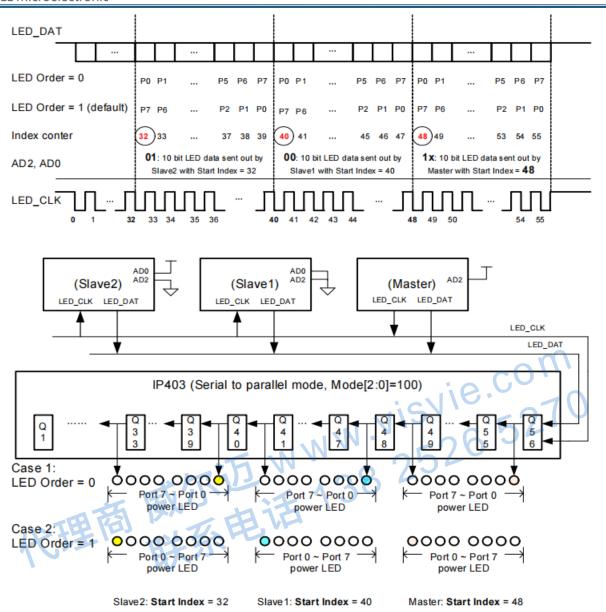

#### **LED Interface**

In auto mode or manual mode, the LED interface can hook up with an IP403 (Serial-to-Parallel LED driver) to display the port status. A port status LED is lit up when TMI7608S allocates power to the port. LED interface is enabled by pulling up LED\_DAT pin with a resister. One TMI7608S can handle 8 LEDs and up to five TMI7608Ss can share one IP403, where one TMI7608S serves as the master to drive LED\_CLK and the others are slaves. AD2 pin defines TMI7608S to be a master or a slave. The index counter in all TMI7608Ss counts from 0 to 55 repeatedly with LED\_CLK after reset and the value of index counter in all TMI7608S are identical. An TMI7608S will send out 8-bit LED information on LED\_DAT when its index counter reaches start index defined in start index register (0x8C). The detail is illustrated in the LED start index register (0x8C) and Figure 9. If there is only one TMI7608S, user can replace IP403 with a 74LS164 to display port status for cost saving. TMI7608S should be configured as a master.

#### **Total Load Power Limit**

TMI7608S has the classification capability to allocate power to each port based on IEEE802.3at, except this, TMI7608S can monitor the total loading power and automatically shut down the lower priority port if total load power is higher than expected power rating. Set the 'PMAXEN' bit high can enable this function, and TMI7608S will compare total load power with the reference power set by PMAX pin. If the total loading is higher the programmed power level and TPMAX over load timer is out, TMI7608S will shut down the lowest priority port among the powered ports. If the total loading power is higher than 150% of programmed limit, the lowest priority port will be shut down at once with about 1ms delay.

#### **EEPROM** controller

When TMI7608S operates in auto mode, the register file can be loaded with some initial value from external EEPROM (24xx series EEPROM, Maximum support to 24C16). TMI7608S reads the EEPROM starting from address 0, parses the contents of the EEPROM command blocks, checks for integrity of the contents, and then writes the designated registers. This process continues until there is either no more data or the integrity check fails. EEPROM is necessary only if user wants to modify the default value of registers in auto mode.

#### **Thermal Shutdown**

If the device's die temperature reaches 150°C (typ), an overtemperature fault is generated and the device shuts down. The die temperature must cool down below 130°C (typ) to remove the overtemperature fault con- dition. After a thermal shutdown condition clears, the device is reset and the TSD event bit is set to a logical 1 (R12h[7]/R13h[7]).

www.toll-semi.com

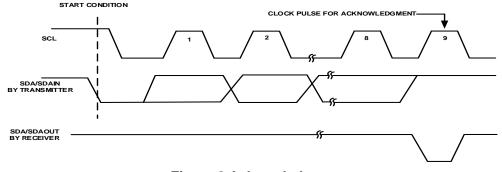

#### **I2C Slave Interface**

Through the I2C slave interface of TMI7608S, host CPU can access the register file in TMI7608S. It consists of SCL, SDAO and SDAI pins, where SCL is Clock, SDAO is Serial Data Output and SDAI is Serial Data Input. This I<sup>2</sup>C interface supports the 7-bit addressing mode of the I<sup>2</sup>C standard. The clock speed can be up to 1 Mbit/sec. There can be up to eight TMI7608S chips on one I2C bus, the LSB 3 bits of the I<sup>2</sup>C address can be assigned with the address pin AD2~AD0. The MSB 4 bits of the I<sup>2</sup>C address are fixed at 1110b. The following diagram is the register read/write cycles of the I2C bus.

I<sup>2</sup>C Register Write 1 Byte Cycle:

| From host to TMI7608S | Start | Device<br>Address | w |   | Register<br>Address |   | Register<br>Data1 |   | Stop |

|-----------------------|-------|-------------------|---|---|---------------------|---|-------------------|---|------|

| From TMI7608S to host |       |                   |   | Α |                     | Α |                   | Α |      |

I<sup>2</sup>C Register Read 1 Byte Cycle:

| From host to TMI7608S                | Start | Device<br>Address | w |   | Register<br>Address |   | Start | Device<br>Address | R | NA Stop           |

|--------------------------------------|-------|-------------------|---|---|---------------------|---|-------|-------------------|---|-------------------|

| From TMI7608S to host                |       |                   |   | Α |                     | Α |       |                   |   | Register<br>Data1 |

| Start Bit = $1 \rightarrow 0$ , Sto  | •     |                   |   |   |                     |   |       | isVI              | S | -070              |

| W = write Bit = 0, R = Read Bit = 1  |       |                   |   |   |                     |   |       |                   |   |                   |

| A = ACK Bit = 0, NA = NO ACK Bit = 1 |       |                   |   |   |                     |   |       |                   |   |                   |

| I2C hus read/write evoles diagram    |       |                   |   |   |                     |   |       |                   |   |                   |

www.toll-semi.com

I2C bus read/write cycles diagram

Figure 5 Serial Interface Timing Details **Table 3. Programmable Device Address Settings**

| DEVICE ADDRESS       |   |   |   |     |     |     |  |  |  |

|----------------------|---|---|---|-----|-----|-----|--|--|--|

| B7 B6 B5 B4 B3 B2 B1 |   |   |   |     |     |     |  |  |  |

| 1                    | 1 | 1 | 0 | AD2 | AD1 | AD0 |  |  |  |

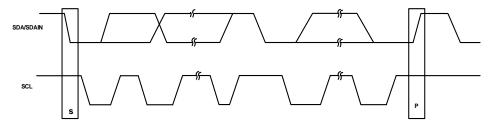

#### **START and STOP Conditions**

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high to low while SCL is high. When the master finishes communicating with the slave, the master issues a STOP (P) condition by transitioning SDA from low to high while SCL is high. The STOP condition frees the bus for another transmission (see Figure 6).

Figure 6 START and STOP Conditions

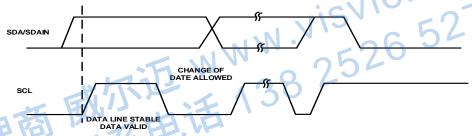

#### **Bit Transfer**

Each clock pulse transfers one data bit (Figure 7). The data on SDA must remain stable while SCL is high.

Figure 7 Bit Transfer

### **Acknowledge**

The acknowledge bit is a clocked 9th bit (Figure 8) that the recipient uses to handshake receipt of each byte of data. Thus, each byte transferred effectively requires 9 bits. The master generates the 9th clock pulse, and the recipient pulls down SDA during the acknowledge clock pulse, so the SDA line is stable low during the high period of the clock pulse. When the master transmits to the TMI7608S, the device generates the acknowledge bit. When the device transmits to the master, the master generates the acknowledge bit.

Figure 8 Acknowledge

Figure 9 LED behavior and system diagram of multiple TMI7608S application

# **Package Information**

### QFN8X8-56

Unit: mm

|        |       |                 |        |        |                           |      | O    |  |  |

|--------|-------|-----------------|--------|--------|---------------------------|------|------|--|--|

| Symbol | Dimen | sions In Millir | neters | Symbol | Dimensions In Millimeters |      |      |  |  |

| Symbol | Min   | Nom             | Max    |        | Min                       | Nom  | Max  |  |  |

| Α      | 0.7   | 0.75            | 8.0    | D2     | 6.55                      | 6.65 | 6.75 |  |  |

| A1     | -     | 0.02            | 0.05   | E2     | 6.55                      | 6.65 | 6.75 |  |  |

| b      | 0.18  | 0.25            | 0.30   | е      | 0.50BSC                   |      |      |  |  |

| С      | 0.18  | 0.25            | 0.30   | Nd     | 6.50BSC                   |      |      |  |  |

| D      | 7.90  | 8.00            | 8.10   | L      | 0.35                      | 0.40 | 0.45 |  |  |

| Е      | 7.90  | 8.00            | 8.10   | h      | 0.30                      | 0.35 | 0.40 |  |  |

| Ne     |       | 6.50BSC         |        |        |                           |      |      |  |  |

**Note 1:** All dimensions are in millimeters.

www.toll-semi.com

28

# **Tape And Reel Information**

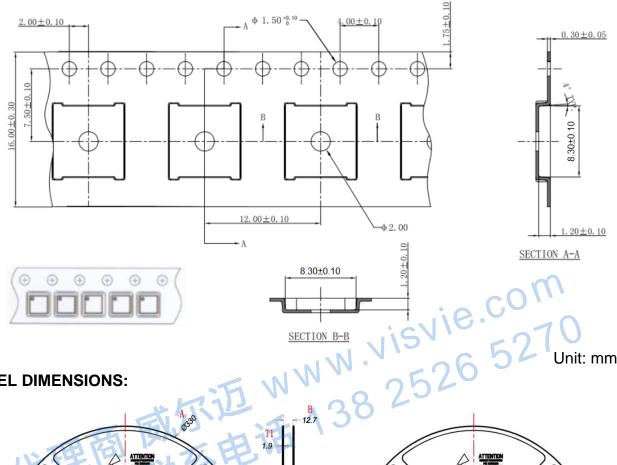

### **TAPE DIMENSIONS: QFN8X8-56**

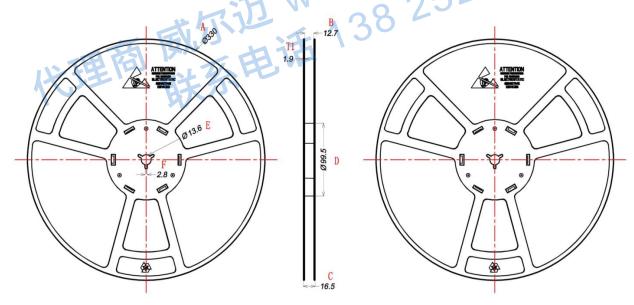

### **REEL DIMENSIONS:**

Unit: mm

| Α       | В        | С        | D          | E          | F       | T1      |

|---------|----------|----------|------------|------------|---------|---------|

| Ø 330±1 | 12.7±0.5 | 16.5±0.3 | Ø 99.5±0.5 | Ø 13.6±0.2 | 2.8±0.2 | 1.9±0.2 |

#### Note:

- 1) All Dimensions are in Millimeter

- 2) Quantity of Units per Reel is 3000

- 3) MSL level is level 3

TMI7608S V0.3 2023.12

# **Important Notification**

This document only provides product information. TOLL Microelectronic Inc. reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time.

TOLL Microelectronic Inc. cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a TMI product. No circuit patent licenses are implied.

All rights are reserved by TOLL Microelectronic Inc. http:// www.toll-semi.com

代理商 威尔近 WWW. Visvie. com 代理商 威尔近 WWW. 2526 5270

30